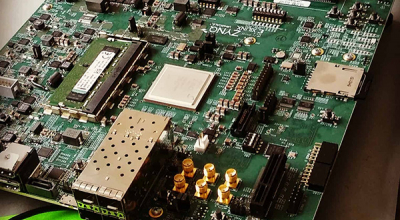

iWave 的 Zynq UltraScale+ MPSoC SOM 支持万兆以太网功能

judy 在 周一, 07/19/2021 - 11:39 提交

以太网技术继续向更高、更优的性能和功能水平不断迈进。万兆以太网 (GbE) 有望满足苛刻的市场需求,提升性能并仍能兼容之前的各种变型。它可以满足高性能实时系统、云计算、零延迟传输系统和高性能嵌入式计算 (HPEC) 的苛刻需求。它也是高速处理器之间和 I/O 通信的可行性选择。

以太网技术继续向更高、更优的性能和功能水平不断迈进。万兆以太网 (GbE) 有望满足苛刻的市场需求,提升性能并仍能兼容之前的各种变型。它可以满足高性能实时系统、云计算、零延迟传输系统和高性能嵌入式计算 (HPEC) 的苛刻需求。它也是高速处理器之间和 I/O 通信的可行性选择。

Xilinx Artix®-7 系列的成本优化型 FPGA ,提供具有业界最高性能功耗比的结构、收发器线速、DSP 处理能力和 AMS 集成。该系列产品采用 MicroBlaze™ 嵌入式软核,支持 1066Mb/s DDR3,特别适用于各种成本功耗敏感型应用,比如软件定义无线电、机器视觉相机和低端无线回传。大电流型号适合 > 4A 的设计,小电流型号适合 < 4A 的设计。

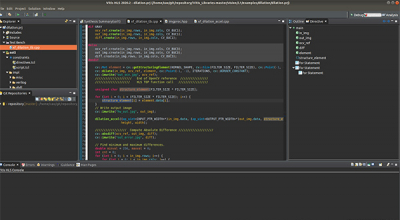

环境条件,首先需要安装opencv3.x版本,这个opencv是在执行test bench的时候才有用,个人理解就是能够生成处理后的图片,方便对比处理效果。不安装并不影响生成RTL kernel。

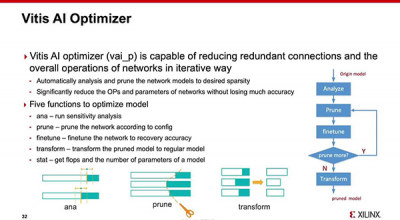

Xilinx 器件及 Vitis/Vitis AI 解决方案可为众多应用加速,包括视频处理、图像预处理、AI 推断以及内存带宽优化等。在本视频中,我们将演示如何使用 Xilinx ZCU104 开发人体检测应用。

在本篇博文中,我们将在“猫和狗”数据库上重复先前第 2 部分中已完成的过程,并且我们将添加一些其它内容。

前提环境:开发板上电后,JTAG模式启动,SD卡已烧写系统文件,JTAG 和UART已连接主机。首先 下载驱动Linux_3.x.x_4.x.x_VCP_Driver_Source.zip

Xilinx 推出 Versal™ HBM 系列,在单个平台上融合了高速存储器、安全连接和自适应计算,面向计算最密集、内存受限、高带宽应用。

近年来,向基于NAND闪存的存储迁移和非易失性存储器快车®(NVMe™)的引入,为技术公司以不同的方式"做存储"增加了许多机会。实时数字业务的快速增长和多样性要求这种创新,以便实现新的产品和服务。本应用说明介绍了BittWare支持FPGA和MPSoC的250系列加速器产品如何用于让客户为下一代物联网和云基础设施构建高性能、可扩展的NVMe基础架构。

赛灵思今日宣布推出 Versal™ HBM 自适应计算加速平台( ACAP ),这是 Versal™ 产品组合的最新产品系列。Versal HBM ACAP 在单个平台上融合了高速存储器、安全连接和灵活应变的计算。该系列集成了最先进的 HBM2e DRAM,可提供 820GB/s 吞吐量和 32GB 容量,与 DDR5 1相比存储器带宽提高 8 倍、功耗降低 63%。

Versal Premium 通过全新的 GTM SERDES 提供了 112G PAM4。 本视频对此项技术进行了概述, 并演示了 SERDES 运行于直接连接铜缆。