第9届!速报名参加这个电子产业趋势和技术展望“爆款”论坛

本篇是利用 Python 和 PyTorch 处理面向对象的数据集系列博客的第 2 篇。我们在第 1 部分中已定义 MyDataset 类,现在,让我们来例化 MyDataset 对象,此可迭代对象是与原始数据交互的接口,在整个训练过程中都有巨大作用。

面对不同的需求,数据中心不再是“以不变,应万变”,数据中心产业迎来变革的新时期。近日,中国IDC圈的记者及其他多家行业媒体,针对数据中心革新、生物计算等问题采访了赛灵思大中华区数据中心业务销售总监 钟屹,以及赛灵思数据中心加速系统架构师 傅垚

当今的设计突破了器件容量和性能的极限,常常为及时满足设计目标带来艰巨的挑战。了解 UFDM(超快设计方法)的最新发展,这是一系列基于工厂专家经验的最佳实践,在过去几年里他们帮助客户解决了最棘手的设计收敛问题,并获得了最佳结果质量。同时,还可了解非常实用的 Vivado 综合与实现技巧,以提升生产力。

目前基于MPSOC的一些参考设计中并没有实现开机画面的功能 ,那在一些带显示屏的产品在设计的时候就需要这一功能,基于原来传统的方式也可以在FPGA中来实现,今天分享一个在PS侧来实现开机画面,以节省PL侧的宝贵资源。

瑞士计时公司基于瑞苏盈科的火星Mars ZX2核心板(基于Xilinx Zynq-7000 SoC)打造了为奥运会等大型体育赛事的计时工作设计的超高精度手持设备PowerTime 3,此设备将会被用于东京奥运会的计时。

软件和 AI 营销副总裁 Ramine Roane 将讨论行业趋势,并带您了解最新的 Xilinx 解决方案和工具。了解 Xilinx 自适应计算如何提高加速应用的标准。

Xilinx Zynq RFSoC 系列最新成员的视频演示:RFSoC DFE 或数字前端。在视频中,我们将展示在没有 CFR 和 DPD 模块的情况下, Zynq DFE 的 ACLR 和 EVM 性能。

本届 CVPR 上,来自北京的赛灵思 AI 研发团队的论文《RankDetNet:深入研究目标检测中的排序约束》成功入选。同时,在 CVPR 期间的自动驾驶研讨会“ Waymo 开放数据集挑战赛”上,赛灵思北京 AI 研发团队又获得“实时 3D 检测”第三名。

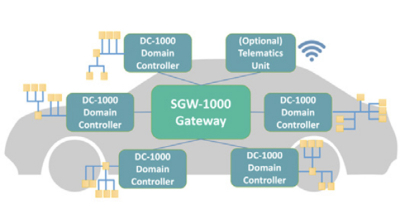

目前,汽车市场对软件定义功能和应用的需求越来越旺盛,行业正迫切需要一种先进的网关,能够提供通用性并为客户提供数据加速和数据分析功能。此外,由于 OEM 车辆和软件定义车辆在需求上存在较大差异,因此需要一种功能更强大且良好平衡的通用型解决方案。