ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

judy 在 周四, 11/12/2020 - 09:37 提交

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

赛灵思公司与三星电子有限公司今日宣布推出三星 SmartSSD® 计算存储驱动器(CSD)。基于赛灵思 FPGA 的 SmartSSD CSD 是业界首款灵活应变的计算存储平台,能够提供数据密集型应用所需的性能、定制能力和可扩展能力。

足不出户,即可了解5G行业最新趋势,以及赛灵思T1 Telco加速器卡、集成硬化IP的Zynq RFSoC DFE、Versal AI Core等5G最新产品与方案。

随着基于云的网络的增加,企业网络中的流量已经大大增加,数以百万计的流量流入和流出企业网络。下一代防火墙安全设备需要高吞吐量的高级安全威胁缓解策略和恶意软件检测功能。下一代防火墙正在从低吞吐量(1-10Gbps)的基于软件的流量检查设备进化为高吞吐量(100-400Gps)的状态流量检查设备,这些设备实现了基于流量的动态网络流量策略规则

11 月 5 日,致力于加速人工智能推断的赛灵思开发软件平台——Vitis AI,在全球电子工程领域知名媒体机构 ASPENCORE 主办的“2020 全球电子成就奖(World Electronics Achievement Awards,WEAA)”评选活动中,荣膺“2020 全球电子成就奖年度软件/工具”。

在一个工程里,有两个Xilinx AXI DMA。其中一个AXI DMA设备是用于调试的。任何时候,其实只使用一个设备AXI DMA设备。软件使用了bperez77_xilinx_axidma的内核和用户态驱动。

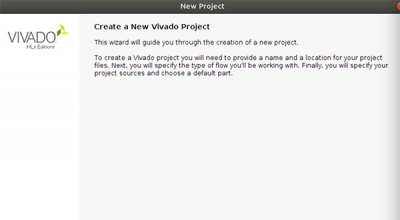

第一个Xilinx Vitis IDE入门helloworld程序

在读取 IBERT 的自适应环路代码时,出现了与 DMONITOROUT 的期望值不同的值。对于 UltraScale+ GTH 收发器而言,签名了一些 RX 均衡自适应环路。用户指南的数字监控器 (DMON) 部分向用户展示了如何读取自适应环路的当前状态。