ZYNQ基础系列(三)VTC+VDMA+Vid_Out核 构建一个简单的显示通路的准备工作

demi 在 周四, 12/12/2019 - 15:46 提交

本文将先介绍三个VIVADO自带的视频输出通路相关的重要IP核,搭建一个比较简单的视频通路,为不久之后的摄像头到显示屏通路打下基础......

本文将先介绍三个VIVADO自带的视频输出通路相关的重要IP核,搭建一个比较简单的视频通路,为不久之后的摄像头到显示屏通路打下基础......

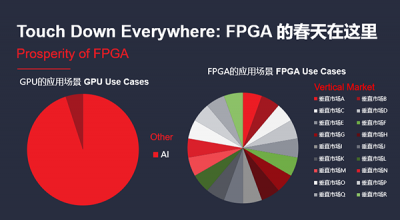

2019 年 12 月 3 日 - 4 日,赛灵思 XDF-亚洲站在北京国家会议中心举办,高效能服务器和存储技术国家重点实验室受邀做主题报告,对研究成果向国内外的与会代表进行展示交流。报告针对当前智慧金融异构加速领域的创新,向听众分享了实验室与 Xilinx 联合成立的“智慧金融科技创新国际联合实验室”的研究情况。

汽车应用作为赛灵思“加速核心市场发展”战略落地市场之一,本届 XDF-亚洲站的 75 场主题演讲和来自数十个现场生态伙伴展示中都有涉及,作为内行的您一定管中窥豹、看出门道了吧?今天,让我们一起来看看赛灵思专家毛广辉发自 XDF-亚洲站现场的点评吧~

赛灵思大中华区数据中心专家级工程师王晓群:面对异构计算的潮流,赛灵思正毫不犹豫地将骨子里的创新与激情释放出来。这种毫无保留源自于公司对于趋势和技术的精准把握,和对业界开发者的信心。

什么是时序约束?泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

2019 赛灵思开发者大会( XDF )亚洲站于北京胜利闭幕。赛灵思总裁兼 CEO Victor Peng 发表了“赛灵思:创新驱动力”为题的主题演讲,分享了公司启动三大战略一年多来所取得的重大成就。

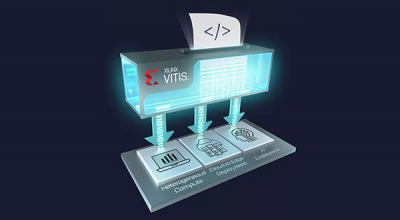

还在为错过XDF上Lab Zone的案例体验而锤头顿足吗?还在为不知道如何部署和使用Vitis与Vitis AI而心灰意冷吗?大家都可以通过以下Vitis Acceleration Lab中精选出来的优秀技术分享案例来学习与跟进,帮助大家指导和使用Vitis。

12 月 8 日,第三届全国大学生 FPGA 创新设计竞赛颁奖典礼在南京市江北新区成功举办。来自江南大学的江南B318团队、来自东南大学的 “CCCTV10” 团队和“串串最好吃”团队获得赛灵思企业特别奖。赛灵思作为协办单位之一,第三次全程参与这项全国性大学生 FPGA 竞赛,继续为竞赛提供从产品到技术培训的全面支持。

描述使用UltraScale™和UltraScale +™器件进行PCB和接口级设计的策略。

RGB 图像转灰度图像的计算,即由当前像素点的 RGB 值计算 YUV 色域的 Y 通道的数值