不会用示波器的Verilog码农不是一个好码农

demi 在 周一, 11/25/2019 - 12:33 提交

在FPGA调试过程中,除了逻辑代码本身的质量之外,FPGA板子上PCB走线、接插件质量等因素的影响也非常重要。在刚上板调试不顺利的时候,不妨拿示波器看一下信号的质量,比如时钟信号的质量、差分信号的质量、高速串行信号的质量等等

在FPGA调试过程中,除了逻辑代码本身的质量之外,FPGA板子上PCB走线、接插件质量等因素的影响也非常重要。在刚上板调试不顺利的时候,不妨拿示波器看一下信号的质量,比如时钟信号的质量、差分信号的质量、高速串行信号的质量等等

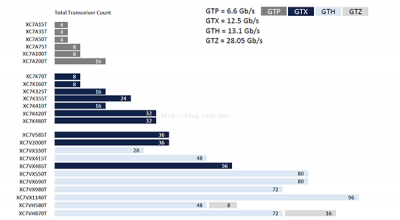

每一个收发器拥有一个独立的发送端,发送端有PMA和PCS组成,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

PCIE的三种事务读写:存储器读写、配置读写、I/O读写

UltraScale™FPGA收发器向导用于配置和简化Xilinx®UltraScale或UltraScale +™器件中一个或多个串行收发器的使用。

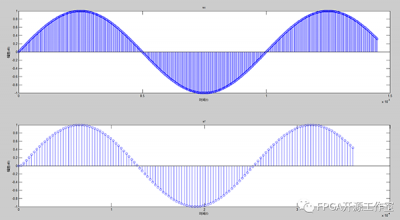

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。在三中我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍抽取。

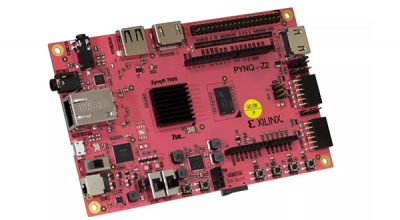

我们为什么要学习 Python?玩转 Pynq 的 9 岁天才儿童要大学毕业了!他就是 Laurent Simons。让人惊讶的是,早在 6 岁时他就开始学习高中课程了........

阻塞赋值:前面语句执行完,才可执行下一条语句;即:前面语句的执行(b=a)阻塞了后面语句的执行(c=b)。即:always块内,2条语句顺序执行。

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同。

Xilinx 与 NTU 联手举办首届女子 Hackathan 2019

嵌入式人工智能自动驾驶领导者魔视智能宣布,将携其基于赛灵思汽车级异构计算平台 Zynq® UltraScale+™ MPSoC 的全新自适应前装量产自动泊车系统亮相赛灵思开发者大会 (XDF)。