Zynq Ultrascale+ 可为工业、汽车及航空市场的混合关键性应用提供确定性处理

judy 在 周四, 05/16/2019 - 14:05 提交

当前的市场需求正迫使我们在所有嵌入式应用中通过使用多核 SoC 增加计算需求,同时需要保存几十年前为单核处理器开发的原有实时代码。实时处理器的性能有限,设计人员通常需要考虑使用应用处理器来获得所需的性能,其代价是牺牲确定性和最坏情况执行时间 (WCET)。

当前的市场需求正迫使我们在所有嵌入式应用中通过使用多核 SoC 增加计算需求,同时需要保存几十年前为单核处理器开发的原有实时代码。实时处理器的性能有限,设计人员通常需要考虑使用应用处理器来获得所需的性能,其代价是牺牲确定性和最坏情况执行时间 (WCET)。

微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序

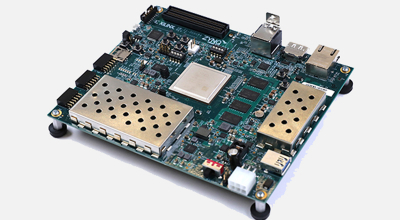

做事情讲究个“谋定而后动”,做研发尤其如此,准备工作一定要做得充分了,需求一定要理解明确了,方可开始吭哧吭哧继续往下干。楼主先准备以ZCU104为平台,实现一个视频处理和传输系统,算是熟悉ZYNQ UltraScale+ MPSoC器件。

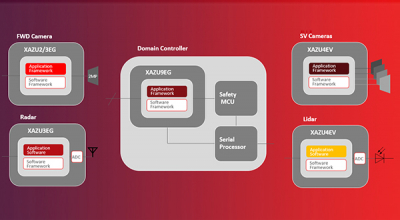

新一代汽车的大量新功能,比如驾驶员辅助等,都需要更大的动能来感知在所有驾驶条件下汽车周围所发生的情况。通过可重编程的高灵活度车辆平台,Xilinx 提供满足这些需求的理想解决方案。

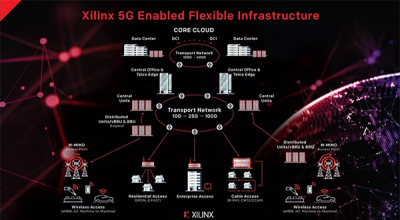

过去 10 年来,云计算成为在全球范围内出现的的一个新兴市场,通过因特网为全球数十亿用户提供计算服务。云计算趋势的发展反映出人们使用计算机方式的根本变化。云技术可为企业提供新的方式,将任务从本地 IT 基础架构转移到优化的远程计算集群,同时也交到云服务供应商的手中

该网络研讨会将概述 Xilinx 和 AWS 物联网各自的技术堆栈,以及两家公司如何合作提供客户可用来为其工业物联网 (IIoT) 解决方案实现跨越式起步的集成型参考设计。 主讲人将引用一个支持 AWS 物联网分布式控制应用的 Xilinx 功能实例