Xilinx出席2019智博会,诚邀合作伙伴沟通洽谈

judy 在 周三, 05/08/2019 - 09:08 提交

5月9日-11日,刚刚结束福州数字中国建设峰会之行的赛灵思,再次受邀高调亮相素有人工智能届小 CES 之称的苏州全球人工智能产品应用博览会 (简称智博会), 除60平米的大型展示区之外,赛灵思大中华区销售副总裁唐晓蕾(Maria Tang)同时受邀在高峰论坛发表主题演讲。

5月9日-11日,刚刚结束福州数字中国建设峰会之行的赛灵思,再次受邀高调亮相素有人工智能届小 CES 之称的苏州全球人工智能产品应用博览会 (简称智博会), 除60平米的大型展示区之外,赛灵思大中华区销售副总裁唐晓蕾(Maria Tang)同时受邀在高峰论坛发表主题演讲。

2019年5月 6日-9日,在拥有2200多年文化历史的中国名城福州举行的第二届数字中国建设峰会上,全球芯片行业的领导企业,FPGA、硬件可编程 SoC 及 ACAP 的发明者赛灵思公司 大中华区销售副总裁 Maria Tang,携手全球及中国本土合作伙伴和用户率团出席,展示了赛灵思解决方案如何作为各类智能应用的强大核“芯”,全面赋能数字中国建设的创新事业

本次视频重点介绍了赛灵思嵌入式软件工具 2018.3 版本的新功能,以及基础架构的重要更新。内容涉及包括 PetaLinux 增强功能,Linux 和 U-Boot 更新以及 MicroBlaze 更新等等。

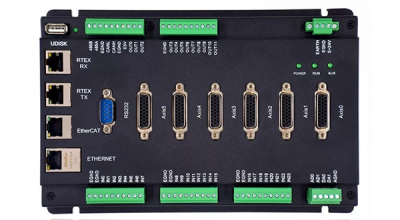

深圳市正运动技术携手自适应和智能计算的全球领先企业赛灵思公司,以及其他基于赛灵思技术提供各种智能方案和产品的业界领先企业一起,共同参展于2019年5月6-8日在中国福州举行的数字中国建设峰会2019。深圳市正运动技术作为智能制造的代表,为与会者展示了3-128轴EtherCAT/RTEX总线的工业互联智能运动控制器的解决方案。

5月6日-9日,自行科技联合全球自适应和智能计算领导企业,赛灵思公司,及其智能产品与方案合作伙伴,共同参加第二届数字中国建设峰会与成果展。公司携国内首款基于深度学习技术的高性能前装量产驾驶员监控系统(DMS)和集成像素级语义分割/雷达融合技术的前向ADAS系统重磅亮相!

作为国内专业的元器件本土代理商和自适应和智能计算的全球领先企业赛灵思公司 (Xilinx, Inc.) 中国唯一的本土代理商,科通集团 携手赛灵思携手多家在不同智能应用领域领先的用户带来各种优秀产品及方案,共同参加:2019年5月6-8日在中国福州举行的数字中国建设峰会2019

预防医学与微创外科手术的发展正在推动内窥镜系统增强功能需求的发展。传统多芯片实现方案会产生时延问题,会对现代内窥镜所需的低延时、高带宽及计算密集型功能造成负面影响。一款典型的内窥镜系统包括具有光源和摄像机头的内窥镜、摄像机控制单元 (CCU) 以及图像管理单元。

MYD-C7Z020 开发板的构建基于 MYC-C7Z020 CPU 模块,该模块是一款基于 ZYNQ 的、Linux 就绪型的小巧 SOM,全面结合 Xilinx XC7Z020-1CLG400C SoC 器件、1GB DDR3 SDRAM、4GB eMMC、32MB 四路 SPI 闪存、千兆位以太网 PHY、USB PHY 和外部看门器