All node

AI算法推陈出新 Xilinx ACAP平台灵活胜出

judy 在 周日, 05/05/2019 - 11:01 提交

一直以可编程技术为发展重点的Xilinx,2018年3月正式启动策略转型工作,凭借数据中心产业连续十年的成长取得好成绩,业绩表现连续十四季成长。面对人工智能(AI)的大趋势,未来已经没有一个架构可以满足所有的应用需求,深度学习算法迭代迅速,传统硬件设计周期赶不上AI发展的速度,灵活弹性的架构才能应付AIoT时代的需求

Zynq UltraScale+ RFSoC ZCU111 评估套件

judy 在 周日, 05/05/2019 - 09:52 提交

Zynq® UltraScale+™ RFSoC ZCU111 评估套件有助于设计人员为无线、有线接入、预警 (EW)/雷达以及其它高性能 RF 应用快速启动 RF-Class 模拟设计.该套件采用 Zynq Ultrascale+ RFSoC,支持 8x 4GSPS 12 位 ADC、8x 6.5GSPS 14 位 DAC 和 8 个软决定前向纠错 (SD-FEC)。

Xilinx 为诊断和临床提供的医疗保健解决方案——机器人辅助手术

judy 在 周日, 05/05/2019 - 09:42 提交

机器人辅助手术是临床外科和医疗保健领域发展最快的项目之一。一些行业专家、临床医生和外科医生认为,机器人在手术中的应用是大势所趋,可实现切口更小、恢复时间短、住院时间缩短、并发症风险降低、失血和疼痛减少。如今,世界上不到 5%的手术使用机器人辅助,预计它将以惊人的速度增长

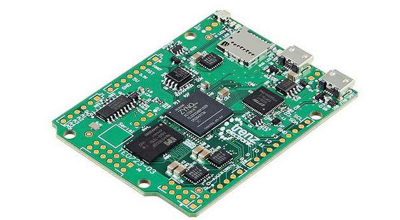

向 Arduino 和 Raspberry Pi 开发板组合添加少许 FPGA

judy 在 周二, 04/30/2019 - 14:23 提交

Arduino 和 Raspberry Pi 开发板是颠覆嵌入式系统开发方式的登峰造极之作。从前,嵌入式系统的开发从硬件开始。项目步骤一般如下:

1. 规范系统要求,包括粗略估计处理速度和 I/O 要求。

2. 选择符合功率、性能和价格要求的适当微控制器或微处理器。