Xilinx 宣布率先引入 HDMI 2.1 IP 子系统

judy 在 周三, 02/13/2019 - 15:05 提交

赛灵思公司宣布已将完整的 HDMI 2.1 IP 子系统引入其知识产权核(IP核)产品组合中,使得各种搭载赛灵思器件的专业音视频设备能够发送、接收和处理高达 8K(7680x4320 像素)的超高清 (UHD) 视频

赛灵思公司宣布已将完整的 HDMI 2.1 IP 子系统引入其知识产权核(IP核)产品组合中,使得各种搭载赛灵思器件的专业音视频设备能够发送、接收和处理高达 8K(7680x4320 像素)的超高清 (UHD) 视频

在HLS中使用帧间差分法生成了IP核,这里讲述如何在vivado中调用IP core

在这篇文章,我们要讲的则是如何透过 AXI_GPIO 来处理 输入 的控制,并让 Cortex-R5 根据不同的输入,在 ps_uart1 输出不同的讯息,以及控制不同的 LED 亮暗。

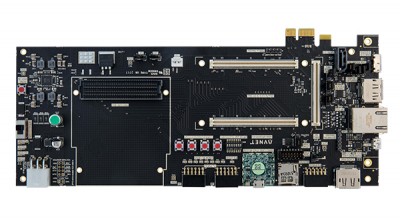

本文档提供了 Xilinx Alveo 数据中心加速器卡的软硬件安装全流程指南。 Avelo 卡符合 PCIe Gen3 x16 规范并采用赛灵思 UltraScale+ 架构,完美适用于加速计算密集型应用,比如数据库加速、机器学习、数据分析以及视频处理等。

Falcon Computing 公司在 XDF 硅谷推出混合云 GATK 管道的 FPGA 加速

当Zynq外挂NAND Flash的时候,如何对MTD进行管理,尤其是坏块管理就变得很重要,最常用的当然是应用于Flash的日志型管理系统:传统的JFFS2及其升级版:UBIFS

采用 FPGA 实现深绿 MPP:一个超动力 Greenplum 数据仓库解决方案

此文章是我在生成IP Core以后,进行网络搭建时出现的License问题的解决方案,在这里跟大家分享一下,希望对大家又所帮助。

背景:ZynqNet能在xilinx的FPGA上实现deep compression

目的:运行zynqNet的代码。

源码地址:https://github.com/dgschwend/zynqnet

项目程序架构,针对我们的项目,我们需要看懂相应的HLS程序和ARM端的程序。

ARM端的程序以_FIRMWARE为准;FPGA端程序以HLS为准。

1. _TRAINED_MODEL

这部分为训练好的caffe模型与预训练的权重。

2. _FIRMWARE

这部分程序针对Zynq 7Z035 ARM processor。make之后是在服务器上运行的,一次迭代需要将近3590ms

make

./test CPU|FPGA indata.bin (-quiet)

本文提出了一种基于CAZAC序列的OFDM时频同步方案,给出了方案各部分的FPGA实现框图和硬件电路实测效果。首先利用时域同步参考符号进行分段相关得出定时估计,然后结合最大似然法进行粗小偏估计,再将同步参考符号和FFT解调变换至频域,利用两个符号中所填充的CAZAC序列的差异性完成整偏估计