【秘籍】Python高效编程技巧

judy 在 周三, 02/20/2019 - 10:26 提交

初识Python语言,觉得python满足了我上学时候对编程语言的所有要求。python语言的高效编程技巧让我们这些大学曾经苦逼学了四年c或者c++的人,兴奋的不行不行的,终于解脱了。高级语言,如果做不到这样,还扯啥高级呢?

初识Python语言,觉得python满足了我上学时候对编程语言的所有要求。python语言的高效编程技巧让我们这些大学曾经苦逼学了四年c或者c++的人,兴奋的不行不行的,终于解脱了。高级语言,如果做不到这样,还扯啥高级呢?

FPGA开发过程中是免不了要用到移位寄存器的,传统的移位寄存器是通过寄存器(或者叫触发器)实现的,占用的是FPGA内部的逻辑资源,当要移位的次数过多时,自然会耗费更多资源。但是如果用LUT(look up table)查找表实现的话就很轻松了

科大讯飞高级架构师江宏武分享FPGA 在 iFLYTEK 中的研究与应用

ug948中提供的官方例程为图像的中值滤波,该设计将一副256*256大小的RGB图像,添加噪声后提取出其中的Y通道,使用C++语言完成中值滤波。该设计将在Simulink环境下进行仿真。本次设计的流程是利用Vivado HLS建立C/C++代码,Export RTL–>System Generator–>Vivado。

本文将介绍Vivado提供的块级综合流程(Block Synthesis Flow),允许设计者将某些全局设置和策略应用于特定的层次结构中,且可以与设计中的其它模块不同。

背景:ZynqNet能在xilinx的FPGA上实现deep compression的网络,FPGA端程序运用传入每层数据运算后存在DRAM上。

目的:读懂ZynqNet的FPGA端的代码。

FPGA端代码经过HLS高层次综合为硬件语言实现在FPGA上。为fpga_top.cpp与fpga_top.hpp

程序包括:

fpga_top

gpool_cache

image_cache

weights_cache

output_cache

processing_element

memory_controller

(数据定义中fpga_top.hpp需要包含了network.hpp与netconfig.hpp)

本文总结了深度学习中常用的八大类型的卷积,以非常形象的方式帮助你建立直觉理解,为你的深度学习提供有益的参考。

用于实时/动态图像处理的 API

前几天折腾zynq下bram作为rom使用,初始化rom时需要用到.coe文件,但在vivado中“generate output products”后,还会生成.mif文件,下面看一下两个文件的内容。

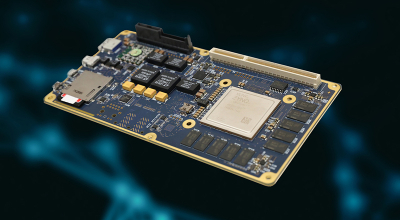

本视频演示了运行在赛灵思 Zynq UltraScale+ MPSoC ZU11 性能板上的 ZF ProAI Gen3 平台。该平台是 ZF (采埃孚公司)与赛灵思联合开发。赛灵思处理器为 ZF 平台带来了低延迟、高性能的 AI 计算