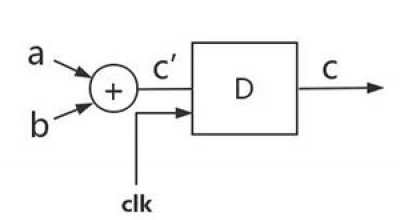

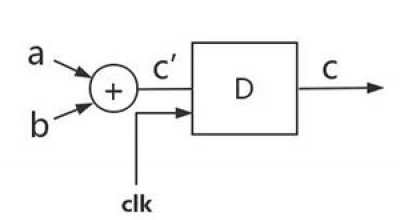

时序逻辑和组合逻辑的区别和使用

judy 在 周五, 08/05/2022 - 08:18 提交

本文介绍两种逻辑的区别以及使用环境。

本文介绍两种逻辑的区别以及使用环境。

Vivado 中的 sigasi 功能特性使用高速缓存,有时高速缓存大小可能高达数百 MB,导致主目录中存储器减少,从而影响 Vivado 性能。

在最近的工作中,又遇到了丢包逻辑的设计。突然想到在FPGA设计中,这是一个非常常见的功能,所以做一个简单的总结。

AMD公布2022年第二季度营业额为66亿美元,毛利率为46%,经营收入为5.26亿美元,经营利润率为8%

本教程涉及到linux版本下安装vivado(vitis)、qt和petalinux的安装。

本文将介绍KPA EtherCAT 主站在ZCU102平台的移植与测试。

传统的C语言数据类型 以8为边界,即数据宽度为8的整数倍,比如32bit,64bit等,相比之下RTL数据的位宽即比较灵活

数据同步一般是指数据从不同时钟域之间传递的过程,是FPGA设计中的基础。数据同步中最常见的问题就是数据在同步过程中被改变

在设计代码的时候,大部分人都是习惯于使用外部的编辑器进行设计,而不是使用vivado自带的编辑器

本文主要着重介绍了两个方面:如何从源码工程构建编译生成镜像文件和如何快速运行demo工程。