想学习FPGA图像处理,这些原理和方法一定要知道!

judy 在 周二, 08/16/2022 - 15:26 提交

图像在采集和传输的过程中,通常会产生噪声,使图像质量降低,影响后续处理。因此须对图像进行一些图像滤波、图像增强等预处理

图像在采集和传输的过程中,通常会产生噪声,使图像质量降低,影响后续处理。因此须对图像进行一些图像滤波、图像增强等预处理

一片RAM中分为许多小格,每一片容量为36k,根据设定的位宽决定了这片RAM可以存放分为几格

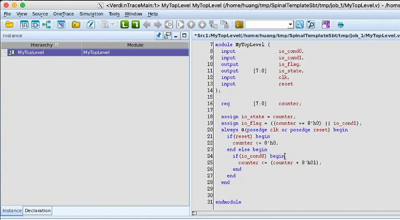

本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。

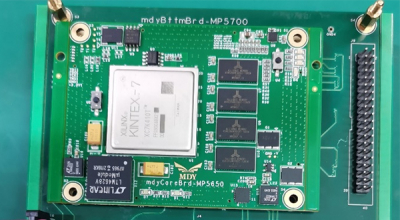

IBERT ip的设置非常简单,只要设置好serdes管脚对应的信息即可,生成的example直接是可以生成bit

本测试实例教程使用IBERT工具对与SFP连接的GTX进行5 Gbps速率下的测试。

对于搞FPGA的人来说,资源和时序的优化,应该是一个永恒的话题

在本系列的前一部分中,我们看到了如何使用以下方法设计同步 FIFO一个双端口、非寄存输出 RAM。

12.16512G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为122.88MHz

无论是FPGA开发还是芯片开发,其中一个重要的环节就是复位设计,本文主要说明FPGA的复位设计

数组在RTL中映射为memory,一般HLS会自动决定最合适的memory,但也支持通过RESOURCE指令具体的memory实现