VCK190 - 如何使用DDR4-DIMM的ECC功能

judy 在 周二, 08/09/2022 - 14:36 提交

在vivado 2021.2的VCK190 boardfile里DDR4-DIMM的DQ width被限制为64bit,不能使能ECC功能

在vivado 2021.2的VCK190 boardfile里DDR4-DIMM的DQ width被限制为64bit,不能使能ECC功能

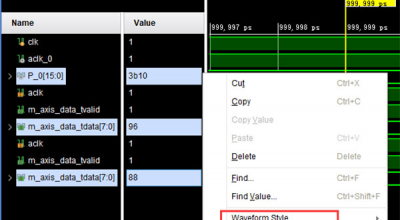

在FPGA的设计里,RR(Round-Robin)调度是一个非常重要的话题。所谓RR调度就是从多个队列中公平地选一个队列进行处理。

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。

一个线速率为3.072G的,输入为20bit,输出为20bit的无协议无编码的4对serdes例程,参考时钟为153.6MHz

接口综合有两种,一种是block-level interface protocol和port-level interface protocol。

让我们以一个简单的例子,FIR 滤波器,来看看如何写出能适配不同型号 FPGA 的代码。

在FPGA的时序分析页面,我们经常会看到Max at Slow Process Corner和Min at Fast Process Corner,具体是什么含义呢?

8月17日,深圳威斯汀酒店,AMD Xilinx 技术日 —— 我们将为您带来最新的自适应计算平台产品更新、技术演讲还有方案展示

先进的数字座舱由 AMD 锐龙嵌入式 V2000 处理器和 AMD Radeon RX 6000 系列 GPU 提供支持

本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考