Xilinx FPGA,“加速”视频质量提升

judy 在 周一, 03/30/2020 - 09:36 提交

本文内容来自Xilinx 张吉帅在LiveVideoStackCon2019深圳站上的精彩分享,他将重点讨论异构计算中非常具有潜力的一部分 —— FPGA,并详细介绍赛灵思以及其技术生态合作伙伴在有关视频加速,图片转码等方面的解决方案。

本文内容来自Xilinx 张吉帅在LiveVideoStackCon2019深圳站上的精彩分享,他将重点讨论异构计算中非常具有潜力的一部分 —— FPGA,并详细介绍赛灵思以及其技术生态合作伙伴在有关视频加速,图片转码等方面的解决方案。

本项目介绍了Sense HAT在PYNQ上的使用。Sense HAT是是为树莓派设计的集成外设板,包含了惯性传感器、湿度温度传感器、气压传感器和一个8×8LED矩阵。这些外设通过I2C总线利用不同设备地址来访问。本项目分成三个部分介绍:LED矩阵显示字符、温度气压传感器读取和惯性传感器数据读取

或许是每个做硬件的厂商都有做软件的心,xilinx发布了他的下一个平台Vitis,也就是硬件和软件分开了(即Vivado和IDE分开了),除了启动方式和使用方法略有区别外,其他操作几乎与上一代Vivado一模一样。本文是试用这个新平台来尝尝鲜。

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。此 IP 只是仿真 IP,将不进行综合(它将在 Pass-through 配置中被连线所替代)。

“灵活应变”是赛灵思经常使用的一个词语。今天,这个词语显得比以往任何时候都更有意义。整个赛灵思大家庭 – 包括我们的员工,我们尊敬的客户,还有我们的合作伙伴们,在这样一个全球COVID-19(新冠状肺炎病毒)疫情蔓延的艰难时期,定义了真正的“自适应能力”和“灵活应变能力”

在本篇文章中,我们将介绍如何使用 Vitis 在 Alveo 板卡上开发和部署硬件加速应用。包括可用资源及文档,如何安装所需的开发工具和软件包,以及如何使用赛灵思 Github 加速用例。视频演示部分会向大家详细展示如何使用 Vitis 图形化界面和命令行流程在 Alveo U200 板卡上进行加速用例的开发和部署

Vitis 是为释放自适应硬件平台的强大威力而打造的全球首个统一软件平台,作为首批学习并掌握Vitis 专业知识的小伙伴们,将成为点燃下一代自适应技术加速创新的星星之火。为此,赛灵思将特别为参与全部课程并完成相关技术测验的优秀学员颁发一份珍贵的学习证书

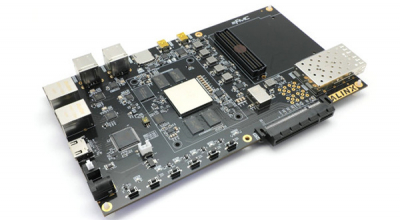

赛灵思隆重发布了世界一流的Zynq®UltraScale +™RFSoC ZCU216评估套件。该套件专门为系统架构师和RF(射频)设计者而设计。这个革命性的平台在具有高能效,高性能和全部软件可编程的开发系统中,为设计者提供了自适应无线电平台的强大功能

作为近年来被普通大众认可的“提升幸福指数”产品,智能门锁这个由欧美国家发起、日韩普及的居家用品在中国市场不断渗透。随着市场用户教育深化、消费升级加速等因素影响,2020 年中国智能门锁市场规模将有望达到 340.6 亿

赛灵思全球分销合作伙伴——全球领先的技术解决方案提供商安富利公司亚洲宣布,其和 AI 软件领域的创新企业 Mipsology 达成协议,将向其亚太区客户推广和销售 Mipsology 的独特的 FPGA 深度学习推理加速软件 —— Zebra 软件平台