ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果

judy 在 周四, 03/19/2020 - 09:23 提交

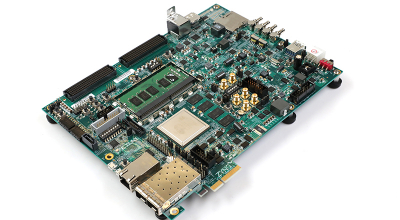

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

基于JESD204数字接口的数据转换器正在兴起,目前渐渐取代了部分基于LVDS接口的数据转换器,这种趋势就如同十几年前基于LVDS接口的数据转换器开始取代基于CMOS接口的数据转换器情形一样。

阿里云的业务之一是为众多第三方厂商处理海量产品图像。由于一些图像内含有未付费广告等多余文本信息,给付费广告业务造成不利影响,因此,为了确保电子商务网站提供一致的体验,需要以 AI 推断对每天数千万幅图像中嵌入的有害文本或多余文本进行检测

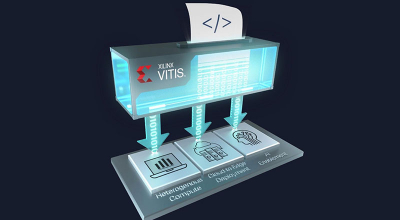

Vitis 被 Xilinx 称为 “统一软件平台”,从目前已了解的情况来看,嵌入式软件开发在 Vitis 上更为简单方便。从 ISE 到 Vivado,再到 Vitis 的升级趋势来看,Vitis 将是未来数年的开发主力。

本视频以 Alveo 加速卡为例,教您快速开始使用赛灵思 Vitis 开发软件进行开发。

软件工程师如何借助赛灵思统一软件平台Vitis将算法提速数倍?

如何快速打造从云到端可自适应的经得起时间检验的应用?

如何快速上手Vitis?

本案例利用PYNQ自定义Overlay驱动Respeaker,实现了一个智能音箱。ReSpeaker是一个四路ADC芯片AC108位转换芯片的四通道麦克风的设备,它支持I2S接口,在本案例中它需要连接到PYNQ-Z2的树莓派接口。

在本视频教程中,您将了解 Aveo 加速卡的 Vitis 基本流程,以及如何使用 Vitis 分析仪分析编译结果。

Vivado设计有工程和非工程两种模式:工程模式是使用Vivado Design Suite自动管理设计源文件、设计配置和结果,使用图形化Vivado集成设计环境(IDE)交互式处理设计。工程模式下,既可以通过图像界面下操作(GUI操作,鼠标操作),也可以通过运行Tcl脚本的方式在Vivado Tcl shell 中运行。

在前面的文章中ZCU106 XRT环境搭建【Xilinx Vitis】,已经生成了用于在Vitis的相关环境。Xilinx在GitHub分享了一个Vitis的应用程序加速开发的教程:2019.2 Vitis™ Application Acceleration Development Flow Tutorials