Kria SOM 加速实现从算法到机器学习模型

judy 在 周三, 05/12/2021 - 10:41 提交

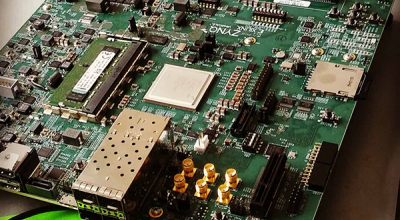

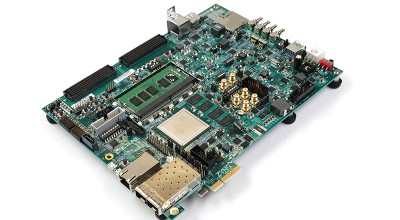

不久以前,从算法到现场机器学习( ML )模型仍然需要经历漫长而复杂的道路。对于一些企业而言,如果能够接触到具有神经网络部署经验的 ML 专家,则可能会有一些选择,但其开发工作却非常耗时。赛灵思依托 Vitis 统一软件平台以及近期推出的 KRIA SOM (System-on-Module),缩短了这一过程。

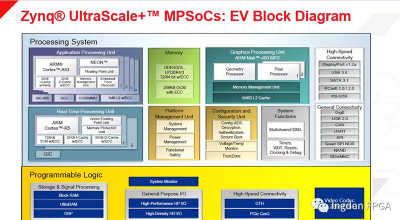

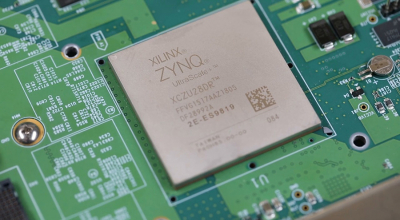

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

不久以前,从算法到现场机器学习( ML )模型仍然需要经历漫长而复杂的道路。对于一些企业而言,如果能够接触到具有神经网络部署经验的 ML 专家,则可能会有一些选择,但其开发工作却非常耗时。赛灵思依托 Vitis 统一软件平台以及近期推出的 KRIA SOM (System-on-Module),缩短了这一过程。

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

在测试MPSoC VCU的编解码时,经常需要使用NV12 YUV文件。YUV文件很大,所以经常依靠解压MP4等文件来产生NV12 YUV文件。 FFMpeg是一个强大的工具,可以用来从MP4文件生成NV12 YUV文件。

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线。比如在文件xfsbl_partition_load.c中,FSBL加载FPGA的bit后会执行下列操作,打开PS和PL之间的接口和信号线

赛灵思车规级 XA Zynq®UltraScale+™ MPSoC 平台提供了特有的自适应能力及高性能计算能力,完美契合宏景智驾 ADCU产品需求,促成了其名为“双子星 (Gemini)”的软硬一体化自动驾驶计算平台 ADCU 的成功推出。

AnDAPT近日推出六种新型PMIC解决方案,以便能够为Xilinx ZU+ MPSoC FPGA系列和Xilinx定义用例的多个电源轨供电。AnDAPT与Xilinx开展密切合作,提供可加速各种工业及计算应用(包括工业(电机控制、可编程逻辑控制、物联网(IoT))、医疗、网络和数据中心设备。)电源研发周期的设计。

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU GIC: CoreLink GIC-400 Generic Interrupt Controller, DDI 0471B, r0p1。

本演示概述了智能相机应用,并指导用户如何设置环境、运行加速应用以及从应用自定义 AI 模型以及生成基准测试数据。

JEDEC LPDDR4 规范 JESD209-4B 的最新发布版本引入了在每次写操作突发前后都将 DQS_c 驱动至高位并保持一段时间的要求(4.13 写操作和屏蔽写操作 DQS 控制信号(WDQS 控制信号)