【FPGA数字信号处理】并行FIR滤波器

judy 在 周一, 09/09/2024 - 14:45 提交

今天介绍一下并行 FIR 数字滤波器的原理以及实现。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

今天介绍一下并行 FIR 数字滤波器的原理以及实现。

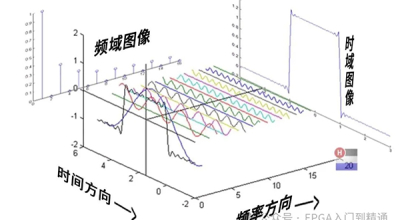

今天,就让我们一同深入这个充满魅力的数字信号处理基础——频域世界。

Verilog中的signed是一个很多人用不好,或者说不太愿意用的一个语法。因为不熟悉它的机制,所以经常会导致运算结果莫名奇妙地出错

这个系列开篇肯定要先了解FPGA的启动流程,试想一下:我想实现MultiBoot,那么我应该在什么时候开始升级,升级失败后FPGA进行了哪些操作

数字电路中,小数可以用两种形式来表示:「定点数」和「浮点数」。浮点数的内容我们下篇文章再讲,本文只讲定点数。

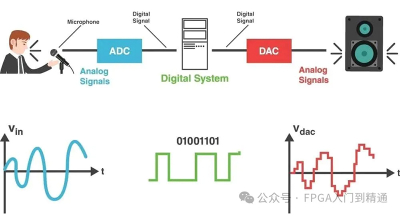

今天,我们将一起探索数字信号处理基础中至关重要的两个概念:连续信号离散化与采样定理。

文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素

本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点

高云半导体此次携车规级产品及方案亮相于汽车芯片专区,高云车规芯片凭借其创新的设计和卓越的市场表现