使用哪种方式可以将 MATLAB 算法转换到FPGA中运行?

judy 在 周五, 08/16/2024 - 09:18 提交

FPGA在进行相关算法计算时,一般都会使用高级语言进行算法验证,目前比较常见的就是 MATLAB ,那么使用哪种方式可以将MATLAB中实现的算哒转换到FPGA中?

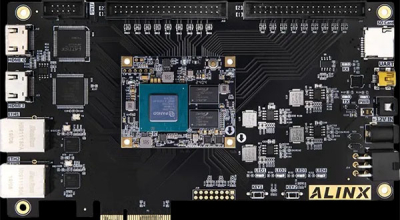

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

FPGA在进行相关算法计算时,一般都会使用高级语言进行算法验证,目前比较常见的就是 MATLAB ,那么使用哪种方式可以将MATLAB中实现的算哒转换到FPGA中?

本系列文章从数字芯片设计项目技术总监的角度出发,介绍了如何将芯片的产品定义与设计和验证规划进行结合,详细讲述了在FPGA上使用IP核来开发ASIC原型项目时

本文将带您了解这三款开发板的主要差异,帮助您根据自身项目需求做出合适的选择。

本次峰会为期半天,将邀请易灵思、安富利、安路科技、瑞苏盈科等FPGA厂商集体亮相分享有关FPGA发展的最新信息,最新确定议程如下

今天来聊一聊Xilinx时钟管理原语,包括它们的定义、分类以及在设计中的应用。

本次研讨会智多晶将首次公开最新研发的SA5T-366,SA5T-200,SA5T-100,SA5Z-30等FPGA产品

本文将深入探讨基于FPGA的简易DDS信号发生器的设计原理和步骤,并提供Verilog代码示例。

本文将带领大家一步步了解并实现一个基于FPGA的简易频率计。

莱迪思Avant-X FPGA集成了许多先进的安全功能,旨在保护IP和器件免受未经授权的访问和攻击,同时又不在SWaP-C(尺寸、重量、功耗和成本)上做出妥协