利用莱迪思Propel赋能基于FPGA的处理器设计

judy 在 周二, 07/02/2024 - 09:43 提交

最新版本的莱迪思Propel(2024.1)进一步简化了开发周期,改善了软硬件设计人员的体验。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

最新版本的莱迪思Propel(2024.1)进一步简化了开发周期,改善了软硬件设计人员的体验。

组件意外停产等供应中断事件会导致原本成功的产品失去应有的价值。这便是为什么英特尔要专注于为FPGA客户提供稳定可靠的弹性供应链。

本文介绍了一种使用机器学习(ML)准确预测FPGA上应用程序执行时间和功耗的方法。

基于Nexus的全新MachXO5D-NX FPGA和Sentry解决方案集合针对不断变化的安全环境进行了优化,具有符合行业标准、加密敏捷和先进的RoT功能

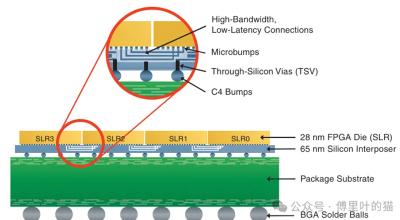

将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载

随着 FPGA 在系统设计中的作用越来越重要,设计也越来越大、越来越复杂,需要更高的逻辑容量和更多的片上资源

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。

本文基于上一篇博文I2C理论知识,通过FPGA实现读写EEPROM(AT24C02)芯片实战操作,进一步了解如何利用HDL实现I2C接口驱动设计。

FPGA作为一种具有硬件可编程及强大计算能力的器件,在前沿创新领域被广泛应用。

现在让我们一起紧随Pluto产品发布会的步伐,揭开Pluto XZU20的神秘面纱,与我们一起探寻未来紧凑而强大的FPGA解决方案!