5G中的DPD技术,怎么玩?

judy 在 周三, 04/06/2022 - 09:42 提交

本文通参考MATLAB的RF仿真工具,展示如何在发射机中使用数字预失真(DPD)来抵消功率放大器中非线性的影响。

本文通参考MATLAB的RF仿真工具,展示如何在发射机中使用数字预失真(DPD)来抵消功率放大器中非线性的影响。

本文介绍MATLAB的混频测试

本次研讨会将介绍在建立 MATLAB/Simulink模 型之后,如何从模型层级进行优化,得到 HDL 代码、与 HDL 仿真器进行联合仿真、硬件在环仿真。

设计创新型无线通信设备需要跨多个学科密切合作。将算法模型部署到 FPGA 硬件可以快速完成原型设计及无线测试,直接从系统级算法自动生成 HDL 代码则可以消除耗时较长的实现和验证步骤。本白皮书通过一个 5G NR 小区搜索设计来说明该过程,介绍将 MATLAB® 算法和 Simulink® 模型直接转换为适用于 FPGA 的 HDL 的工作流。

新兴的 5G 网络依托毫米波频谱运行,这意味着 5G 网络的性能优于 4G 网络,能够以更高的速度、更低的延迟传输更多数据。毫米波频谱技术发展前景广阔,但也使设备制造商面临大量设计挑战。例如,相比低频信号,毫米波频谱信号更易因大气及其他物体的阻隔而衰减。

领域专家和硬件工程师运用 MATLAB® 和 Simulink® 开发原型和生产应用程序,以部署到 FPGA、ASIC 和 SoC 设备。

本视频将介绍Unified Model Composer和System Generator Tool。

.mif 和 .coe 是 FPGA 设计中常用的存储文件,用于 ROM、RAM 等存储器数据的加载,常见的还用在 DDS 信号发生器和 FIR 滤波器的设计中。 .txt 文件主要用于 Matlab 和 FPGA 的联合仿真,比如在滤波器的设计中,可以使用 Matlab 先把加噪声的信号写入到 .txt 文件,然后 FPGA 仿真中在 Testbench 中读取该信号源的数据

本讲使用两个 DDS 产生待滤波的信号和matlab产生带滤波信号,结合 FIR 滤波器搭建一个信号产生及滤波的系统,并编写 testbench 进行仿真分析,第五讲、第六讲开始编写 verilog 代码设计FIR滤波器,不再调用IP核。

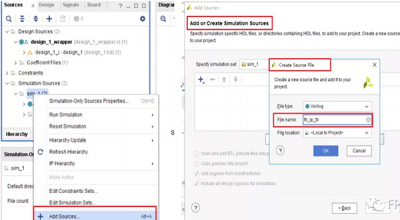

本讲使用matlab产生待滤波信号,并编写testbench进行仿真分析,在Vivado中调用FIR滤波器的IP核进行滤波测试,下一讲使用两个DDS产生待滤波的信号,第五讲或第六讲开始编写verilog代码设计FIR滤波器,不再调用IP核。