【视频】Vitis 为您的应用注入新的活力

judy 在 周三, 08/12/2020 - 15:57 提交

在本次网络研讨会上,您将了解 Vitis 环境,以及该环境如何在 Xilinx 平台上实现嵌入式软件和加速应用开发。

在本次网络研讨会上,您将了解 Vitis 环境,以及该环境如何在 Xilinx 平台上实现嵌入式软件和加速应用开发。

各位开发者小伙伴请听题:

请问,Vitis 从入门到实践需要几步?

这个过程比大家想象中简单

答案是:只需四“部”

为什么是四“部”?

答案马上揭晓

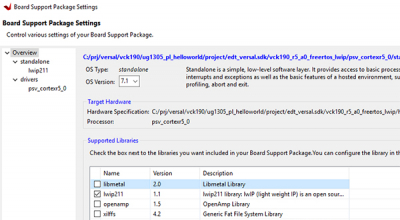

Xilinx的SoC在业界应用非常广泛。对应的开发工具SDK也很成熟。在SDK里,每一个baremetal工程,对应一个BSP工程,它包含一些Xilinx提供的公共模块,比如硬件的驱动、freertos、LWIP等。在BSP工程的右键菜单中,选择BSP setting,可以配置BSP工程包含的的公共模块。

“人间四月芳菲尽”

在这春暖花开复工复产的时节

赛灵思 Vitis 每周一课迎来了压轴大戏

Vitis AI开发环境由Vitis AI开发套件组成,用于在Xilinx硬件平台(包括边缘设备和Alveo加速卡)上进行AI推理。 它由优化的IP内核,工具,库,模型和示例设计组成

不想考考自己的自学能力,顺便提个官方证书吗?

上一期的“Vitis/Vitis AI 每周一课.第二讲”,各位开发者小伙伴认真复习了吗? 随着春暖花开全国复工复查稳步推进,咱们的“Vitis/Vitis AI 每周一课”也来到了的关键环节。今天,小Xi 继续为大家带来第三讲内容 —— Vitis AI 的新特性和开发流程

该视频介绍了如何在 Vitis 命令行流程中进行 GDB 调试。视频前半部分简要介绍了流程。简介之后有一个有关在 Vitis 中进行 GDB 调试的演示。

疫情期间是真爽,睡觉睡得我啥也不想干,本来也琢磨着继续更新,无奈开工就很忙,天天只想睡觉,自从爽了一个月,我就只想睡觉,看来我要买点亚麻籽油提提神了,碰巧最近有网友问他的双核没法正常工作,我试了下,是可以的,但是这当中也遇到点bug,好吧,开始干活吧

在网络培训、大数据和 ML 研究三方面快速发展的推动下,所谓“深度学习”正迅速成为主流。这种说法在嵌入式视觉应用中体现得最为明显,其最终目的是教会机器“领会”。嵌入式视觉应用的范围似乎是无穷无尽的,从确保生产线零缺陷的机器视觉摄像头,到监控交通、检测盗窃和灾难的杆装“智慧城市”摄像头