关于Xilinx SelectIO,你知道什么?

demi 在 周一, 01/20/2020 - 10:08 提交

Xilinx SelectIO IP是为了将LVDS传输过来的串行信号变为并行数据。

Xilinx SelectIO IP是为了将LVDS传输过来的串行信号变为并行数据。

锐文科技 CTO闫燕:由于带宽的提升,比如升到25G,甚至100G 的情况时,普通的CPU是没有办法满足网络上的业务的,它需要绑定几个CPU核来做网络加速。而我们的方案可以节省CPU的资源,把CPU本身做的网络上的业务卸载到FPGA里来做,从而大大提升CPU的效率。

不知不觉之中,大家发现可能机器(手机,电脑)可能比您自己更懂您,在您浏览网页和采购商品的时候,给您推荐的往往都很契合自己某一方面的特点和需求。这个变化就是得益于后台运行着的推荐算法。正因为有了 FPGA 强大的计算能力,让这样的海量检索与分析可以让互联网内容供应商以用户毫无察觉的速度将之付诸实现。

2020年1月15日,自适应和智能计算的全球领导者赛灵思公司(纳斯达克股票代码:XLNX)在位于北京市朝阳区安定路5号院的中海国际中心新办公室,举行赛灵思北京办公室乔迁庆典,隆重庆祝公司进驻新址。

在数据驱动的人工智能摧枯拉朽般冲击各种应用、衍生无数奇思妙想的今天,赛灵思前沿技术研究与学术合作部门隔空召唤:“Time to Innovation, Time to Paper ” —创新的时候到了,发布学术论文的时候到了!

随着 4G 和即将到来的 5G 时代,互联网上每天都在不断产生大量的图像和视频内容,为了保证网络环境的健康,内容提供商必须对平台产生内容进行严格的检测,避免违规违法内容流入互联网。而随着人工智能(AI)时代的到来,图像智能处理系统开始逐渐替代基础的审核人员。

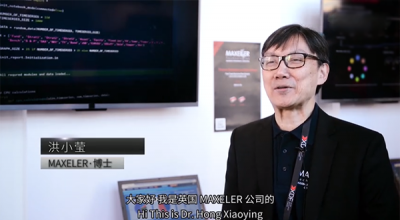

在 2019 XDF(赛灵思开发者大会)上, Maxeler 公司洪小莹博士为大家现场展示了其基于 Alveo 加速卡的 CVA Calculation (信用风险评估调整)的方案。

大数据时代呼唤算力的革命,未来的“计算”将会是什么样?作为引领下一代自适应 AI 技术的全球领导者,赛灵思如何规划和布局?现在真的是软件开发者的天下了吗?

Xilinx对Clock的管理如分频,倍频等没有使用IP,而是直接调用了相关原语MMCME3_ADV,在这里MMCME3_ADV原语是针对UltraScale的器件的,7系列的器件相关原语名称为MMCME2_ADV。这个规则和LVDS的serdes等原语一致。

xilinx文件后缀说明