APB3接口应用-v1

judy 在 周五, 09/13/2024 - 09:47 提交

APB3是一个低功耗低成本接口。所有信号在时钟上升沿传输,每次传输需要两个时钟周期。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

APB3是一个低功耗低成本接口。所有信号在时钟上升沿传输,每次传输需要两个时钟周期。

安路科技PH系列FPGA定位高性价比可编程逻辑市场,针对高带宽应用场景,能够在保持低功耗的前提下,提供同类更佳的收发器和信号处理功能

工业领域的工厂长期以来一直使用数字数据来监视和控制生产设施。工厂、数据中心和商业建筑中的大型网络系统一直在将其数字信息网络的边缘越来越近地推向现实物理世界

Verilog中的signed是一个很多人用不好,或者说不太愿意用的一个语法。因为不熟悉它的机制,所以经常会导致运算结果莫名奇妙地出错

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度,是不同的

FIFO是FPGA项目中使用最多的IP核,一个项目使用几个,甚至是几十个FIFO都是很正常的。通常情况下,每个FIFO的参数,特别是位宽和深度

本文将详细介绍如何通过NOC使用CPM访问片上内存(OCM)

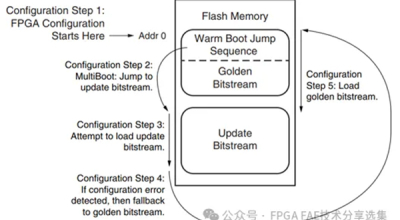

Multiboot是指多镜像启动,比如在FPGA的加载flash里面存放2个或者多个FPGA的配置文件,每个配置文件都可以单独完成FPGA的逻辑配置

文章从介绍使用预先定制功能即IP核的必要性开始,通过阐述开发ASIC原型设计时需要考虑到的IP核相关因素

本文将深入探讨光纤传输 PCIe 领域,这一解决方案有望解决数据中心激增的带宽需求。我们将探讨资源限制、延迟挑战和能耗。