同步FIFO和异步FIFO

judy 在 周三, 08/08/2018 - 16:38 提交

1.定义

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

1.定义

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

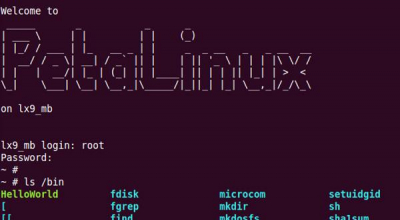

前言

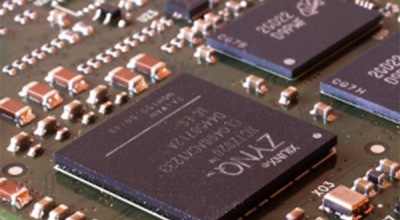

PetaLinux 工具提供在 Xilinx 处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件。理想适用于提升设计生产力,该解决方案与 Xilinx 硬件设计工具协同工作,为 Zynq® UltraScale+™ MPSoC、 Zynq®-7000 SoC、和 MicroBlaze™ 简化了 Linux 系统的开发。

本文是该系列的第8篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程;第7篇介绍了其中数据类型的选择与位宽截断的问题。本文将对其中使用到的Reinterpret和Convert模块进行详细介绍。

MATLAB是美国MathWorks公司出品的商业数学软件,用于算法开发、数据可视化、数据分析以及数值计算的高级技术计算语言和交互式环境。MATLAB和Mathematica、Maple并称为三大数学软件。它在数学类科技应用软件中在数值计算方面首屈一指。无论是做项目还是写论文,我们都会遇到把Matlab画的图形(默认为matlab自带的图像格式.fig)转换为其他格式并导出的问题。

作者:Manuel Mota,Synopsys公司模拟IP部产品营销经理

简介

这是学习SDSoc的第二个入门实验,通过EMIO点亮连接在PL上的8个LED。与上一个实验不一样,在这一个实验中,由于ZedBoard平台中没有使能EMIO,因此想直接通过SDSoc编写程序驱动MIO是不行的,所以这一个实验需要自己搭建包含EMIO的平台。

本文是该系列的第7篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程。不过仍然有些问题需要解决:

1. 如何选择一个最合适的数据类型(以最少资源达到性能需求)?

2. 如何选择系统的输出位宽(保证信号不失真)?

作者:OpenS_Lee

1背景知识

在我们的FPGA设计项目中,硬件的诊断和校验可能会占去超过30%—40%的FPGA开发时间,FPGA的debug也是FPGA设计中重要的一环。掌握并灵活运用FPGA设计工具的debug功能也是加快FPGA设计的关键。

Vivado:2016.4

Linux:Ubuntu16.4

ZYNQ:xc7z020

下载文件名称

2016.4-zed-release.tar.xz

device-tree-xlnx-xilinx-v2016.4.zip