Vivado HLS 入门(二)

judy 在 周二, 08/21/2018 - 17:42 提交

作者:OpenS_Lee

1 概述

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

作者:OpenS_Lee

1 概述

对于FPGA编程时的v文件中的寄存器,在SDK编程时需要一些读写操作,以实现PS与PL部分的信息交换。下面用一具体例子记录所需要的步骤 。如若有误请指正。

DCI与内部参考电压

FPGA中有符号数和无符号数的加法运算

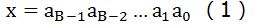

首先定义一个B比特的二进制数:

verilog HDL表示正数就按一般的规则即可,这里主要讲如何表示负数?

zynq AXI是很重要的内容,本篇仅是简单的介绍。大量参考了其他书籍。

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4 版本。

1.AXI总线

ZYNQ有三种AXI总线:

作者:葛兴

cortex-M0是ARM公司的一款开源内核,以低功耗著称,本文提纲挈领的讲述了用FPGA实现SOPC的流程。

1、开源核心

从头开始,在ARM官网上注册,下载ARM cortex M0的源代码以及大量的参考学习文献。

DDR3:使用流程

一. 配置过程

1>首先找到IP核

1.添加debug核的合理方法是在源代码中添加(*mark_debug="true"*),综合后,打开综合结果,set debug内这些标记的信号全部在网标内,不会被优化掉。如果不在代码里加这些标记,直接在综合结果里添加net,很多感兴趣的信号会被优化掉,且残缺不全。

作者:Kevin Zhang

在学习FPGA一段时间之后,昨天和师兄交流面试题,题目中问CLB、LUT的概念,我都是不知道这是什么?经过学习,总结如下内容:

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单介绍一下Vivado下显示指定路径时序报告的流程。

1.打开布局布线后的结果