Vivado RTC实时时钟系统设计

judy 在 周一, 08/28/2023 - 10:19 提交

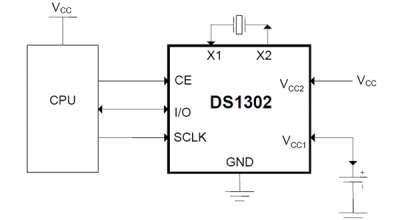

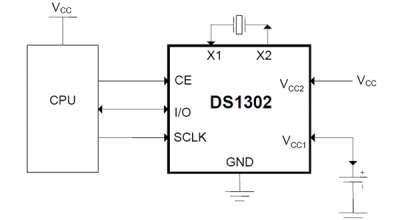

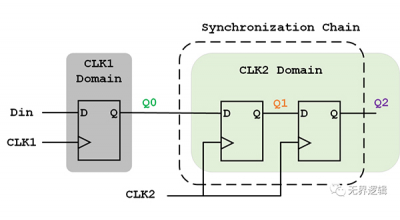

我们一起学习一下RTC的驱动

我们一起学习一下RTC的驱动

用支持PYNQ框架的PYNQ-ZU平台,与人工智能来一场聊天

AMD-Xilinx MPSoC 和 Versal ACAP 系列均具有复杂的内部电源结构

本文将深入研究JTAG和SWD,比较它们的特点、优劣势以及适用场景

EEPROM是一种特殊形式的闪存,其应用通常是个人电脑中的电压来擦写和重编程

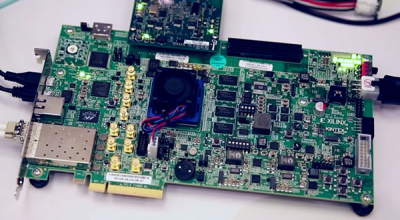

本文重点讲解单bit跨时钟域的处理方法

Vitis™ HLS 利用 AMD FPGA 提供的独特优势和特性,为高性能设计优化 C 代码

FPGA属于数字电路范畴,工作中我们会碰到时钟频率,信号速率

本文介绍了 LOS 状态机行为,并提供了解决问题的方法

IDC预计,2027年中国AI投资规模有望达到381亿美元,全球占比约9%