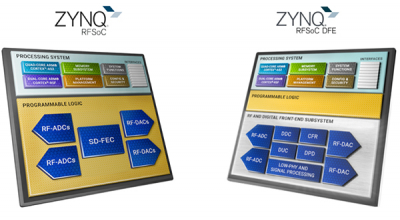

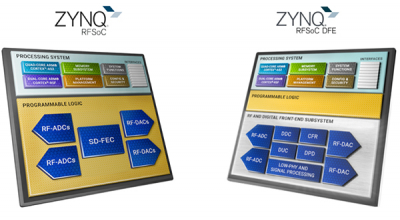

Zynq UltraScale+ RFSoC器件介绍

judy 在 周一, 05/22/2023 - 14:43 提交

本文介绍一下Xilinx公司新一代Zynq UltraScale+ RFSoC器件

本文介绍一下Xilinx公司新一代Zynq UltraScale+ RFSoC器件

本实验主要介绍使用PS端来完成ZYNQ串口打印输出的功能

本文涵盖了在 Versal GTY 和 GTYP 中使用模式生成器和检查器时对以下操作的限制

本文将演示如何在 Versal AI Core 系列 VCK190 评估套件上从 USB 辅助启动模式启动 Linux

每个模块的 GTH 规格略有不同。相比于商用级 K26C,工业级 K26I 存在一些限制

通过XTmrCtr_GetValue获取时间戳,是以时钟周期为单位的

HBM将多个DDR芯片堆叠在一起,所以也是个3D结构;每个die之间通过TVS和microbump方式连接

FPGA 技术支持灵活开展现场编程和再编程,无需通过设计修改来重建互连结构

客户为AMD Xilinx SoC创建了PetaLinux工程。需要定制PetaLinux中的FSBL

本文介绍利用TI公司TXS0108实现FPGA IO Bank接不同外设IO接口电压转换