ZYNQ 程序固化到QSPI FLASH实验

judy 在 周一, 05/29/2023 - 10:08 提交

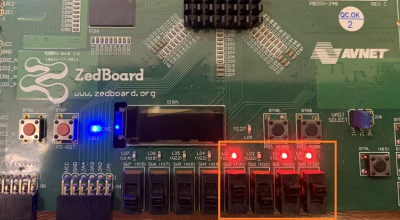

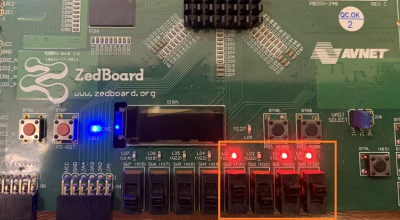

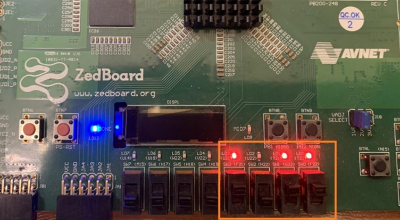

本实验教程主要指导大家如何将程序固化到QSPI FLASH中,并让ZYNQ芯片上电启动自动加载QSPI中的程序

本实验教程主要指导大家如何将程序固化到QSPI FLASH中,并让ZYNQ芯片上电启动自动加载QSPI中的程序

在数学中,假如要判断一个数x是否在[a,b]内还是一件比较简单的事情

使用Intelligent Design Runs,Versal™ 自适应 SoC 的平均 QoR 提升 8%

本实验将为大家介绍如何在Vivado中构建 AXI总线类型的IP核

新XA AU10P和XA AU15P处理器符合汽车标准,并针对驾驶辅助系统传感器应用进行了优化

Artix UltraScale+器件壮大了 AMD车规级、功能安全验证、高度可扩展的 FPGA 及自适应 SoC 阵营

AMD Vitis 调试代码时,BSP代码的某些应该被执行的行,没有被执行

使用ZYNQ最大的疑问就是如何把PS和PL结合起来使用。本实验使用两个AXI GPIO的IP核

现场展示基于 AMD EPYC™ 处理器和 Xilinx FPGA 的现代网络的解决方案