一个工程师有关FPGA项目的感言

judy 在 周一, 12/20/2021 - 09:34 提交

一个工程师有关FPGA项目的9个感言

一个工程师有关FPGA项目的9个感言

本文介绍目前常见的几种可以提高机器学习模型的可解释性的技术,包括它们的相对优点和缺点。

本文从ROS 2机器人专家的视角提出建议,即全面考虑ROS 2的硬件加速。这一视角能体现:优化流程中、流程内、网络内(含底层)的ROS 2运算图交互;以及加速ROS上运行的应用。

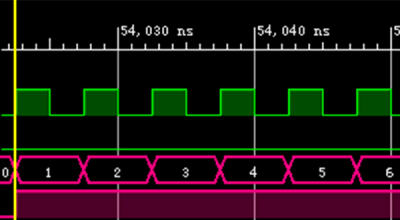

SystemVerilog 中新增了一种数据类型,即联合体。联合体支持您以多种不同方式来引用数据中的某一部分。本文将介绍联合体的使用方式以及综合工具针对联合体的处理方式。

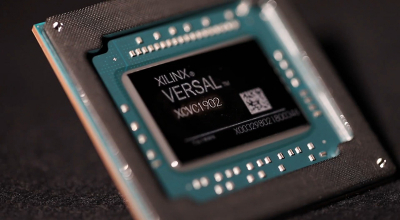

Xilinx 技术支持实时数据处理并可延长功耗,助力 DroneHunter 保护公共基础设施。

是时候准备好收看一场冲击视觉的大战并为之欢呼了!在与 Rev Robotics 的合作中,赛灵思是战斗机器人 Switchback 的赞助商。

设计自动化会议最近在旧金山举行。在演讲中,涵盖了广泛的领域——例如,设计自动化算法领先技术、商业 EDA 工具的新功能、技术和财务趋势和预测以及行业标准活动。下面附上一份来自笔者对 DAC 的印象盘点。

赛灵思 Versal® 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。

了解嵌入式软件(如 Linux、Xen Hypervisor 和免费实时操作系统)与构建工具(如 Yocto 和 PetaLinux)在 2021.2 发布周期中的新增特性。 该视频将详细介绍在该发布周期中所有的新增功能与修改内容。

实验任务:将输入数据(data_in)存入ddr,然后读出,验证输入输出数据是否相等。