开发者分享 | 如何动态更改 UltraScale/UltraScale+ GTH/GTY 线速率

judy 在 周五, 08/07/2020 - 09:44 提交

本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。

本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。

本次由信息技术新工科联盟主办,Xilinx、东南大学,西南交大联合承办的暑期学校已经在8月3日落下帷幕。从7月20日到8月3日这十五天间,超过1200名学员在全世界各地通过互联网参与了这一次暑期学校,累计了100小时的实践,超过10位讲师的精彩分享。

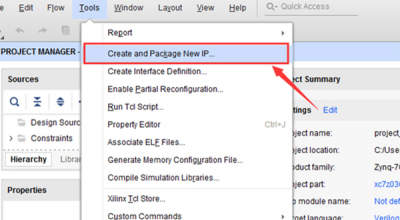

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过M_AXI接口对数据进行读取操作,此时设计一个基于AXI-Slave接口的IP进行数据传输操作就非常的方便

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

Vitis AI1.1 系列教程

Python是一种很棒的语言,语法简单,无需在代码中搜索分号。对于初学者来说,Python是入门最简单的语言之一。Python有大量的库支持,你还可以安装其他库来增加自己的编程经验。学了一阵子之后,你可能会觉得:为如此简单的操作写大量的代码有些令人困惑。

Xylon 首席执行官 Kovačec 介绍了一种用于实际 HIL 仿真的车载 HIL(Hardware-in-the-loop)视频记录仪。 他还说明了 Xilinx 技术如何助力这一独特功能集。

本期AI观察室,让我们走近赛灵思AI算法总监田露,走进一个女工程师的世界,了解一个她和她所代表的女工程师的实践与思考。。

赛灵思今天宣布,搭载赛灵思车规级芯片平台 Zynq® UltraScale+™ MPSoC 的百度 Apollo 自动驾驶计算平台 ACU 于伟创力中国苏州工厂正式量产下线,这款量产的 ACU 硬件平台将率先应用于 Apollo Valet Parking( AVP )自主泊车产品。

智能网联是汽车行业发展最重要的趋势之一,包括自动驾驶和车联网两个主流方向。各国政府包括中国政府在内,都在积极地制定智能网联技术路线并不断完善本国的智能网联标准体系。不可否认,智能网联技术及其标准体系都将对汽车座舱发展产生深远的影响。