深维加入元脑生态,携手浪潮打造FPGA高性能图像处理方案

judy 在 周四, 05/28/2020 - 09:53 提交

近日,浪潮与北京深维科技有限公司签署元脑生态战略合作协议,双方将联合打造基于FPGA的高性能图像处理解决方案,共同为AI方案的行业落地和智算中心高效运营扫清最后一公里障碍。

近日,浪潮与北京深维科技有限公司签署元脑生态战略合作协议,双方将联合打造基于FPGA的高性能图像处理解决方案,共同为AI方案的行业落地和智算中心高效运营扫清最后一公里障碍。

4倍的清晰度,除了带来更完美的感官体验之外,在我们工程师眼里那就是无尽的延迟和呃算法效率的降低,尤其是习惯于传统的在软件中处理图像的小伙伴们。抓狂有木有?

说在前面,本文分享了两个视频,从 DFX 的布局规划,再到布局规划的进阶。两个视频,20分钟帮您快速掌握 DFX 的布局规划...

SK 电讯的业务核心是一个名为 AIX 的 AI 推断堆栈,它负责处理从语音识别到视频分析的各种业务,这就需要一个单独的底层计算平台。SK 电讯的 AI 推断检测服务名为 TView™,可实时监测 200 万个商用和家用摄像头系统,在发生物理入侵的情况时立即派遣安保人员

《电子发烧友》2020 “中国人工智能卓越创新奖”评选重磅登场,赛灵思及其两大平台同时入选提名!

随着赛灵思 Alveo 自适应计算加速卡的发布,数据中心各种工作负载开启了自适应计算加速的历程。本期小编特整理了有关 Alveo 的一批中文文档,以供各位随时下载和查阅。

本次网络研讨会描述了两个使用 Zynq UltraScale + RFSoC 进行无线通信的设计示例。 首先,让我们回顾一下针对大规模 MIMO(64x64),100MHz LTE(ORAN 7.2 split)的设计,并解释其实现和选型性能数据。

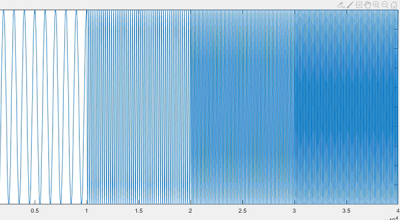

在Matlab中,做短时傅里叶变换需要使用函数spectrogram,而在Matlab2019中,引入了一个新的函数stft,下面我们就来看下这两个函数都如何使用。

首先通过上面的简单分析,我们应该很清楚一件事:TCP协议很复杂,光握手过程就需要“三次握手、四次挥手”的复杂过程,不是特别适合FPGA的纯逻辑实现,因为用FPGA实现以太网通信的主要目的就是进行低延时的传输数据,而一旦设计规模达到一定量级,FPGA实现通信的优势便不复存在,转而体现出“性价比”低的劣势

数字信号对载波信号的振幅调制称为振幅键控,即ASK。在2ASK调制系统中,数字信息只有0和1两种,所调制的载波信号的幅度变化状态也只有两种:无载波输出时代表发送0;有载波输出时代表发送1。在4ASK调制系统中,数字信息就有00、01、10、11四种,需要载波信号幅度的4个电平状态表示