真香!Yocto 铁杆用户转粉 PetaLinux 的三大理由

judy 在 周四, 05/21/2020 - 10:00 提交

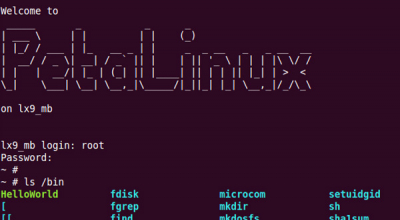

PetaLinux 是一套直接构建在 Yocto 项目顶层的定制工具,用于实现与赛灵思平台的集成。因此,在某种意义上 PetaLinux 仍属于 Yocto。但赛灵思更进一步,通过提供一套额外的工具,简化了开发流程,使新手使用起来及其方便

PetaLinux 是一套直接构建在 Yocto 项目顶层的定制工具,用于实现与赛灵思平台的集成。因此,在某种意义上 PetaLinux 仍属于 Yocto。但赛灵思更进一步,通过提供一套额外的工具,简化了开发流程,使新手使用起来及其方便

您的数据中心工作负载是否正亟需一个灵活应变的计算基础设施?一个可以通过定制跟上算法的快速演进突破、可以不断扩展以处理指数级增长的海量数据、可以在保持低功耗的同时大幅提升性能从而降低在云端运营托管产品、提供服务的基础设施?

云计算已经成为了一种新的计算范式。对于云计算而言,虚拟化是一项必不可少的技术,通过将硬件资源虚拟化,可以实现用户之间的隔离、系统的灵活可扩展,提升安全性,使得硬件资源可被充分利用

通过本次研讨会,您将更详细地了解 Alveo 加速卡的优异性能,以及来自 Deepoly 公司的 ThunderImage 超高性能图像处理方案的加速能力。

Xilinx 提供了一个基于命令行的自包含实用程序,称为 xclbinutil。 您可以将其用于 Xilinx 加速器二进制容器文件(.XCLBIN)。本视频将带您了解使用 xbutil 检查、报告并修改 xclbin 内容的基本步骤。

在证券交易领域,行情数据瞬息万变、盈利机会转瞬即逝,因此“低时延”是金融交易追求的核心目标。这也正是Enyx公司备受金融行业青睐的原因:2019年,著名交易技术提供商Vela宣布Enyx为美国股票提供下一代基于FPGA的股票行情自动收录器设备,该设备将延时减少一半以上。

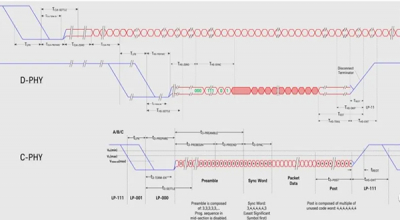

MIPI是移动领域最主流的视频传输接口规范,没有之一,目前应用最广泛的是MIPIDPHY和MIPI CPHY两组协议簇,其中CSI-2主要用于图像接入,DSI-2主要用于图像输出。本文主要以CSI-2为例进行仔细说明,DSI-2雷同,举一反三即可。

本文介绍了Wireshark的快速FPGA实现FFShark。其结果是一个紧凑的、相对便宜的直通设备,可以插入任何正在运行的100G网络中。数据包将在FFShark中传输,不会中断,并且附加的延迟最小

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。Vivado 提供了预编译的 UVM V1.2 库。请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。本文随附了 1 个简单示例,可供您下载解压使用。

调制就是把要传递的信号“搬运”到规定的频率附近,从技术上说,天线的尺寸和电磁波的波长差不多的时候,才能获得较高的发射效率,假设信号是10MHz,那么波长为30m,这么长的天线显然是不现实的。因此需要把信号调制到较高的频率,减少天线的尺寸