赛灵思又一新款 16nm FPGA 面世, 专为速度而生!

judy 在 周一, 05/25/2020 - 17:41 提交

在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求

在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求

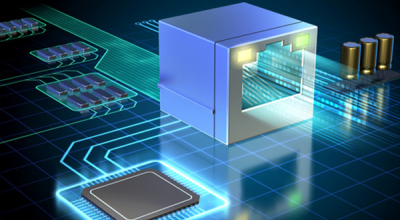

随着高带宽内存(HBM)的发展,FPGA正变得越来越强大,HBM 给了FPGA 更多能力去缓解再一些应用中遇到的内存带宽瓶颈和处理更多样的应用。然而,HBM 的性能表现我们了解地还不是特别精准,尤其是在 FPGA 平台上。这篇文章我们将会在HBM 的说明书和它的实际表现之间建立起桥梁

Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是休眠,就从DDR读出系统状态,恢复系统

本案例来源于第三届全国大学生FPGA创新设计竞赛中江南大学的OpenHEC lab团队,他们的作品基于PYNQ开源软件框架。PYNQ框架提供了完整的访问FPGA资源的Python library,通过高层次的封装,让开发者通过Python API就可以轻松调用FPGA内的模块或算法,加速产品开发部署

为什么UDP协议在FPGA实现时很受欢迎,最主要一个原因就是简单,简答到什么地步呢?UDP协议只是在IP的数据服务之上增加了复用和分用的功能和查错检验的功能。

Xilinx今天宣布推出旗下新的20nm耐辐射Kintex UltraScale XQRKU060系列FPGA,该系列可望在诸多太空级应用的下一代设计中找到很好的定位。

为了辅助Xilinx热门产品20nm Kintex UltraScale KU060 FPGA,Teledyne-e2v现在可提供高度优化的多通道模数转换器(ADC)和数模转换器(DAC)解决方案。它们有各种不同等级类别可供选择,最高级别是高可靠性耐辐射的宇航级,适用于卫星通信、地球观测、导航和科学任务

EFuse 具备一次性可编程特性,即只要使用特定密钥将“熔丝 (FUSE)”熔断,就无法再使用任何其他密钥对其进行编程。 EFuse 广泛适用于各种量产器件,在本文中我们将为大家演示一个典型情境,即客户希望向第三方供应商提供采用 AES 编程的 FPGA 的情境

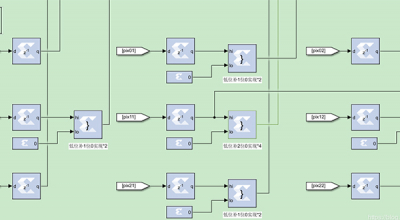

锐化即在图像上增强显示图像内容的边缘成分。根据边缘成分的计算方法,常用的方法有高斯滤波锐化和拉普拉斯滤波锐化。高斯滤波锐化将原始图像 x 减去高斯滤波(相当于低通滤波)后得到的平滑图像 gaussian(x)

在嵌入式系统里,以太网是一个基本的接口,既用于调试,也用于数据传输。所以在单板调试过程中,以太网是一个基本的任务。如果以太网工作正常,也可以说是一个重要的里程碑。Xilinx MPSoC支持多个网卡,应用成熟,下面是常见的调试思路。