【视频】在 Vitis IDE 中构建 Linux 应用程序

judy 在 周一, 05/11/2020 - 10:40 提交

该演示将指导用户完成使用 Vitis™IDE 创建和执行 Linux 应用程序所涉及的步骤。

该演示将指导用户完成使用 Vitis™IDE 创建和执行 Linux 应用程序所涉及的步骤。

本案例支持CameraLink Base/Full模式、彩色/黑白相机。 此开发详解基于创龙ZYNQ Z-7045/Z-7100评估板TLZ7xH-EVM展开。

随着人工智能和5G的兴起,数据处理对芯片的算力和带宽要求更高。为了布局未来,助力人工智能和5G,赛灵思也推出了自己的FPGA加速芯片-ACAP。ACAP是一款基于7nm工艺,集成了通用处理器(PS),FPGA(PL),math engine以及network-on-chip的革命性芯片。

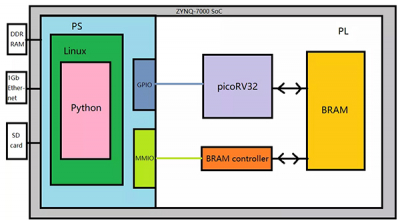

RISC-V-On-PYNQ Overlay实现了在PYNQ-Z2板上的RISC-V处理器及工具链集成,并提供了完整的RISC-V源码与设计流程,得益于PYNQ软件框架,其支持在Jupyter Notebook对RISC-V进行编译、调试与验证,即可以在Jupyter Notebook上编写一段C/C++/RISC-V汇编程序,将编译后的二进制文件放到picoRV32上运行

本篇博文涵盖了配置设备树以将外设和第三方应用详细信息添加到 PetaLinux 工程中的基本流程。在某些情况下,设备树无法生成相关外设所需的所有必需信息,例如,以太网 PHY 信息。在此类情况下,您需要手动将此板级信息和特定开发板信息添加到设备树文件 (system-user.dtsi) 中。

成为公民科学家不是梦!闲置的计算资源不仅用于精确地建模重要蛋白质的结构,还用于设计新蛋白质,让我们一起参与抗击COVID-19!

简要概述 Yocto Project, 以及如何将其用于构建面向 Xilinx 平台的嵌入式 Linux 发布。

FPGA中DSP资源是宝贵的且有限,我们在计算大位宽的指数、复数乘法、累加、累乘等运算时都会用到DSP资源,如果我们不了解底层的DSP特性,很多设计可能都无法进行。逻辑综合往往是不可控的,为了能够充分利用DSP资源,我们需要对DSP48E1有所了解

今天, 赛灵思宣布,正在全球四所最负盛名的高等学府设立“赛灵思自适应计算集群( Xilinx Adaptive Compute Clusters,XACC )”。赛灵思诚邀全球顶尖高校加入 XACC 项目,在采用了赛灵思最新自适应计算加速技术的集群上合作开展尖端 HPC 研究。

如今,在以数据为中心的世界里,网络在数据传输方面的性能正在一步步逼近极限。网络应用需要支持数量不断增多的用户连接、扩大支持的带宽范围、降低它们的时延....

Enyx提供基于FPGA的解决方案,为网络应用的开发提供便利。