【视频】DFX 培训系列课程 - 高级布局规划(中文字幕)

judy 在 周二, 05/19/2020 - 09:30 提交

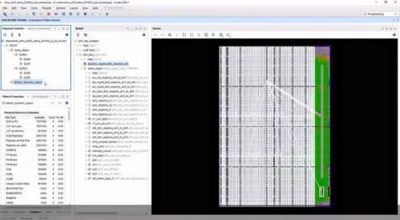

本视频解读 DFX 布局规划基本信息视频,介绍了扩展布线区域的使用。这项 Vivado 功能面向 UltraScale 和 Ultrascale+ 器件,可改善 DFX 设计结果,设计人员创建其布局规划时应考量如何运用此功能

本视频解读 DFX 布局规划基本信息视频,介绍了扩展布线区域的使用。这项 Vivado 功能面向 UltraScale 和 Ultrascale+ 器件,可改善 DFX 设计结果,设计人员创建其布局规划时应考量如何运用此功能

本周,IBM声称,其神经计算机系统达到了每秒120万帧的训练时间,创下了最新记录。IBM在AI模型训练上实现了大突破,可与最先进的技术相匹敌。网友对此表示简直不敢相信!

上期我们分享了王伟老师的 技术文章解析(上),本期将会给大家带来下集解析,Ultra96v2petalinux 2019.2软件平台设计与调试和Vitis AI Linux加速平台的介绍。

作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

本视频围绕 UltraScale 和 UltraScale+ 架构,回顾了 DFX 布局规划基本信息;并提供了通过创建更优化的布局规划来改善设计结果的策略和技巧。

在仿真验证中,SV语言不能很好的描述复杂的计算或者流程关系,使用软件语言(比如C)就比较方便。那么当我们使用C描述了这些关系后,如何在基于SV的仿真环境中使用呢?有两种方式,一种是将C编译为可执行文件,利用系统函数进行调用。另

各位开发者小伙伴请听题:

请问,Vitis 从入门到实践需要几步?

这个过程比大家想象中简单

答案是:只需四“部”

为什么是四“部”?

答案马上揭晓

初识XILINX,是PYNQ-Z2。当时刚学完学校的数字电路课程,对FPGA并不了解,学校课程也仅仅是用VHDL验证了一些基础的FPGA实验,例如生成一个n进位序列码。并不知道FPGA有这么广阔的应用。在一次王伟博士的培训上,我第一次接触到了PYNQ。在讲座中,我运行了一个PYNQ的demo。通过USB摄像头检测边缘处理

赛灵思嵌入式处理产品组合中的赛灵思嵌入式软件堆栈组件简介。

VCU TRD 2019.2配套有多个硬件工程。每个硬件工程中的PL设计不一样,需要的devicetree的节点不一样。PetaLinux根据XSA/HDF文件,生成对应的pl.dtsi。换XSA/HDF文件,新的pl.dtsi可能增加或者减少了devicetree的节点