MII2RGMII IP核使用设计举例

judy 在 周一, 06/01/2020 - 15:52 提交

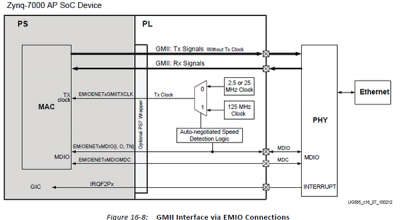

本例程将 PS 的 ETH1 通过 EMIO 方式引出, 通过 EMIO 引出的 ETH 为 GMII 接口, 将其与 GMII to RGMII IP 核连接后转换成 RGMII 接口,然后与外部子卡中的 88E1512 芯片连接。在 PS 端通过 SDK 自带的 lwip echo server 例程通过子卡,以 RJ45 电口与 PC 机实现 TCP 网络通信

本例程将 PS 的 ETH1 通过 EMIO 方式引出, 通过 EMIO 引出的 ETH 为 GMII 接口, 将其与 GMII to RGMII IP 核连接后转换成 RGMII 接口,然后与外部子卡中的 88E1512 芯片连接。在 PS 端通过 SDK 自带的 lwip echo server 例程通过子卡,以 RJ45 电口与 PC 机实现 TCP 网络通信

Xilinx的28nm、16nm SoC在业界应用非常广泛。最近也发布了7nm的SoC器件Versal VC1902和对应的开发板VCK190。Versal是新一代的异构计算平台,包含A72、R5、及内部管理用的CPU。Versal的软件开发工具是Vitis。

时延敏感网络(TSN, Time Sensitive Network)是指能保证时延敏感流的服务质量,实现低时延、低抖动和零丢包率的网络。时延敏感流可分为周期时延敏感流(PTS, Periodic Time Sensitive),比如工厂里的循环控制指令、同步信息,和非周期/零星时延敏感流(STS,Sporadic Time Sensitive),比如事件告警信息。

这一期我们将给大家带来的是第三届全国大学生FPGA创新设计竞赛特等奖作品——基于PYNQ的散射成像相机CC Cam。该作品由来自东南大学的陈欣玥,雷弈,刘可同学设计完成。她们的作品同样基于Xilinx的PYNQ开源软件框架,同时也使用Xilinx的高级综合工具HLS设计了加速算法IP核。

本文介绍如何利用赛灵思 Alveo 卡实现应用加速的简介,包括阐述基本架构方法、识别适用于加速的代码以及利用软件 API 以最有效的方式来管理存储器并充分发挥 Alveo 卡的强大作用。

本次网络研讨会概述了 Zynq UltraScale+ RFSoC 及其在有线电视接入远程 PHY 节点中的应用。我们将首先为世界上唯一集成模数转换器的硬件可编程片上系统提供技术概览,并提供关键性能指标。随后,我们将讨论其在远程 PHY 节点上的应用,该节点利用 Xilinx 合作伙伴 Calian SED 提供的关键 IP 块。

本篇博文旨在演示其构建方式及其用于实践 IP 的机制。我觉得这部分内容值得讲一讲,因为只要您能够充分理解测试激励文件,就可以将其作为有效的模板来用于将 RF Data Converter IP 构建到自己的仿真设置中。

构建产学合作平台,培养新工科全栈人才。

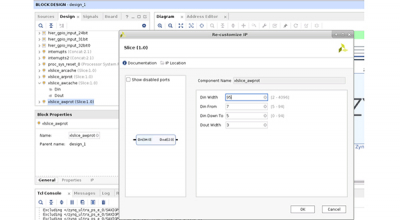

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

通过上面其他章节的介绍,网口千兆通信,可以使用TCP或者UDP协议,可以外挂PHY片或者不挂PHY片,总结下来就有下面几种方式完成通信