今年的 LVS 线上峰会看什么?Xilinx 带您领略自适应视频处理技术与方案

judy 在 周四, 06/04/2020 - 09:38 提交

在今年即将开幕的 LiveVideoStackCon 2020线上峰会上,作为自适应计算的引领者赛灵思再次受邀出席,并将为广大视频/图像处理从业人员带来全新的“构建自适应视频基础设施”的主题演讲。主题演讲将涵盖技术角度、经济角度的多项研究

在今年即将开幕的 LiveVideoStackCon 2020线上峰会上,作为自适应计算的引领者赛灵思再次受邀出席,并将为广大视频/图像处理从业人员带来全新的“构建自适应视频基础设施”的主题演讲。主题演讲将涵盖技术角度、经济角度的多项研究

疫情肆虐,全球经济全面遭受重创且持续低迷。然而,近日中国自动驾驶领域、嵌入式人工智能自动驾驶先锋企业魔视智能,Motovis (赛灵思在中国自动驾驶领域的重要合作伙伴之一),却逆势迎来 A2 轮融资成功的利好消息,融资金额高达一亿元人民币!

本文描述赛灵思 Alveo™ U200 和 U250 加速器卡的规格。

得益于人工智能的发展,它在机器人、物联网和智能个人助理(如Siri和Alexa)等方面创造了惊人的发展。那什么是人工智能呢?人工智能最简单的定义是:收集有关世界的数据,并利用这些数据进行短期和长期的预测。

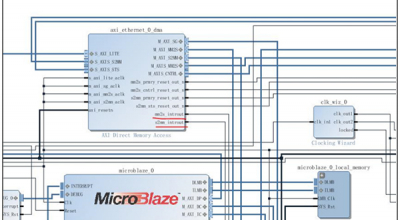

lwip 是瑞典计算机科学院(SICS)的 Adam Dunkels 开发的一个小型开源的 TCP/IP 协议栈。实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用。LwIP 是 Light Weight (轻型)IP 协议,有无操作系统的支持都可以运行。LwIP 实现的重点是在保持 TCP 协议主要功能的基础上减少对 RAM 的占用,它只需十几 KB 的 RAM 和 40K 左右的 ROM 就可以运行

赛灵思的文档繁多,本来可以用简单的方法能够实现,却没有简明的文档进行说明,给新进者带来困扰,下面我来介绍下用Vivado工具定义管脚的两种方法。

Linux下,可以在设备树里保留一段内存,留给用户自己管理和使用,Linux保证不会使用保留内存。在使用中,有人发现,保留内存不能使用非对齐的方式访问。经研究,如果在保留内存时,声明了“no-map”属性,Linux会把这段内存映射为strongly order模式,不支持非对齐的方式访问。

GTX是kintex-7系列FPGA内部的高速数据收发器硬核模块,专门用于FPGA与外部的高速数据通信,目前许多常用的高速协议(比如JESD204、PCIE、SATA、SGMII接口的以太网等)的实现都需要用到GTX。GTX的基本内容以前介绍过了,这里不再叙述。该篇主要记录两片FPGA利用各自的GTX实现高速数据的收发过程

Xilinx 公司的芯片有一整套命名规则,可以通过相关文档查阅。

区块链具有广泛的互联网应用。它可通过设计来分散,因此是许多传统事务处理系统的替代方案。为了使区块链系统可行(可扩展性、可互操作性和可持续性),与区块链相关的复杂耗时/耗电的加密工作应该转移到加速系统中。我们的解决方案是一款安全的公共密钥基础架构引擎,可用来卸载计算密集型公共密钥工作,比如签名生成与验证