【周末创客】电机控制

judy 在 周一, 06/08/2020 - 14:09 提交

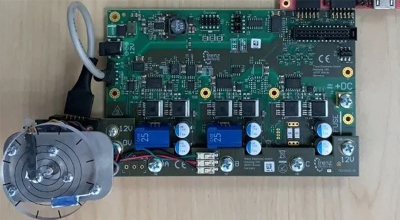

IIoT-SPYN是一个基于IIoT-EDDP开源平台和PYNQ软件框架的项目,它展示了如何在PYNQ开源框架下对电机进行控制、监视、捕获数据、可视化和分析。PL侧包含了对电机控制、状态采集的模块。在PYNQ中加载比特流后,就可以访问到这些已实现好的模块,对电机进行控制和状态检测。

IIoT-SPYN是一个基于IIoT-EDDP开源平台和PYNQ软件框架的项目,它展示了如何在PYNQ开源框架下对电机进行控制、监视、捕获数据、可视化和分析。PL侧包含了对电机控制、状态采集的模块。在PYNQ中加载比特流后,就可以访问到这些已实现好的模块,对电机进行控制和状态检测。

振幅键控信号的解调主要有包络检波和同步检测两种方法,后者又被称为相干解调。相干解调需要提供与输入同频同相的载波信号,通常需要采用锁相环技术实现载波信号的提取,较为复杂,这里采用非相干解调的方法实现ASK解调,只需要将输入信号经过整流滤波即可得到基带信号。

本课程内容参考XILINX 官方文档PG046。这个IP支持Kintex®-7, Virtex®-7 FPGA GTX 和GTH 收发器,Artix®-7 FPGA GTX 收发器, Zynq®-7000 GTX and GTX收发器。Aurora 8B/10B IP core可以工作于单工或者全双工模式。IP CODE 的使用也非常简单,支持AMBA®总线的AXI4-Stream协议。

XAPP1247 是对应使用屏障镜像时的多重启动 (Multiboot) 和回退 (Fallback) 的示例应用。本篇博文提供了一种屏障定时器流程测试方法以及使用此方法时可能出现问题。

LWIP可以通过硬核实现或者软核实现,具体要看FPGA的选型,其中硬核可以通过硬核自带的GMAC通过直连PHY或者EMIO扩展到PHY都可以实现相应功能,同时硬核也可以通过AXI总线与相应的IP相连然后再同外部PHY连接实现相应功能。这部分Xilinx官方提供详细的文档xapp1306-ps-pl-ethernet-performance-lwip和测试例程

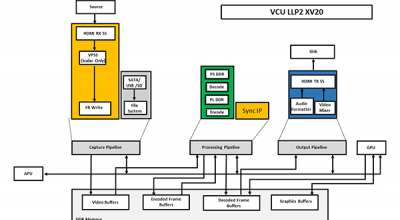

运行 Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display,可以测试HDMI输入输出,和VCU的低延时编码。Xilinx wiki的文章MPSoC VCU TRD 2019.2 - Xilinx Low Latency PL DDR XV20 HDMI Video Capture and Display以H.264和4K分辨率为例。

下面记录H.265和1080p分辨率的运行命令。

在VIVADO的实现的布局中,可以利用PBlock将某一个或某几个Cell(模块单元)固定在Device的固定区域上。如此,可以实现该模块内部的时序收敛,并且,该工具对于可重配置工具的使用也是必不可少的

赛灵思今日以线上会议形式举行了主题为“创‘新’正当‘适’”的大中华区核心市场中国媒体沟通会。在会上,赛灵思大中华区销售副总裁唐晓蕾阐述了赛灵思对数据作为“新基建”核心的洞察,分析了数据万有引力作用下,“新基建”七大核心领域从云到边缘智能计算的机遇与挑战,以及赛灵思所引领的自适应计算与“新基建”的完美契合和光明前景

2020年5月,赛灵思中国汽车市场联盟成员魔视智能(Motovis)宣布 A2 轮融资成功,融资金额高达一亿元人民币。资本市场的青睐,初创公司的激流勇进和脱颖而出,让我们再次把“自动驾驶距离我们到底有多远”的话题提上议程。

本期研讨会将通过一些设计实例来带您了解 Vitis 的主要特性,并掌握如何在 Alveo 加速卡上使用 Vitis 实现加速设计的流程;同时还将系统地介绍一下 Vitis 的主要设计资源。

适合哪些听众