ZYNQ入门实例——三种GPIO应用、中断系统及软硬件交叉触发调试

judy 在 周五, 03/13/2020 - 09:20 提交

Xlinx的ZYNQ系列SOC集成了APU、各种专用外设资源和传统的FPGA逻辑,为ARM+FPGA的应用提供助力,降低功耗和硬件设计难度的同时极大提高两者间传输的带宽。之前在研究生课题中使用过ZYNQ搭建环路系统对算法进行板级验证

Xlinx的ZYNQ系列SOC集成了APU、各种专用外设资源和传统的FPGA逻辑,为ARM+FPGA的应用提供助力,降低功耗和硬件设计难度的同时极大提高两者间传输的带宽。之前在研究生课题中使用过ZYNQ搭建环路系统对算法进行板级验证

如今随着技术的进步,各类嵌入式应用对于架构本身的设计灵活性与功耗性能比提出了更加严苛的要求。瑞萨电子推出了基于Xilinx Zynq-7000的电源时钟管理方案,通过集成了Xilinx基于28nm Artix®-7或Kintex®-7的可编程逻辑,从而实现了出色的功耗性能比与最大的设计灵活性

FPGA 在系统中逐渐由配角变成主角,从普通的胶合逻辑扩展到业务处理,从应用于原型验证扩展到大规模应用于量产设备中。今天的可编程平台已经是最多拥有数百万六输入查找表的强大处理器件

有图 有数 有 真相

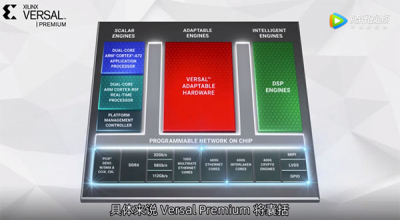

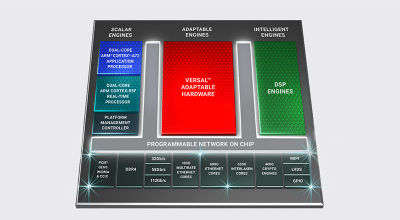

本视频由赛灵思公司 SerDes 系统工程和应用高级总监 Chris Borrelli 向您详细介绍 Versal Premium 系列的技术特性。

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

今天上午,FPGA发领头羊赛灵思公司以在线发布形式宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium,这款FPGA堪称是史上最强大FPGA,它有高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台

赛灵思今天宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium。Versal Premium 系列具备高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台。Versal Premium 专为在散热条件和空间受限的环境下运行最高带宽网络,以及那些需要可扩展、灵活应变应用加速的云提供商而设计

体验 Xilinx 面向网络与云加速所推出的全球带宽最高、计算密度最高的自适应平台。最新的 Xilinx ACAP 提供了功耗优化网络硬核的突破性集成,可实现最高速、最安全的网络 。Versal™ Premium 系列旨在解决高带宽网络在散热条件和空间受限的环境下运行的挑战,并满足云提供商的计算需求。

本文以FZ9A计算卡为例(盒子和其它版本计算卡同样适用),介绍如何使用EdgeBoard进行深度学习应用开发。