AI加速的前前后后

judy 在 周三, 03/04/2020 - 15:32 提交

做深度学习加速器已经两年了,从RTL设计到仿真验证,以及相应的去了解了Linux驱动,深度学习压缩方法等等。今天来捋一捋AI加速器都涉及到哪些领域,需要哪些方面的知识。可以用于AI加速器的主要有三种不同架构的器件种类:CPU,GPU,AI芯片/FPGA。

做深度学习加速器已经两年了,从RTL设计到仿真验证,以及相应的去了解了Linux驱动,深度学习压缩方法等等。今天来捋一捋AI加速器都涉及到哪些领域,需要哪些方面的知识。可以用于AI加速器的主要有三种不同架构的器件种类:CPU,GPU,AI芯片/FPGA。

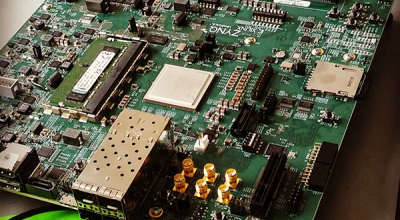

在Zynq®UltraScale +™设备中提供基于1G和10G以太网的示例设计。

本文精心筛选了最能展现 Python 语法之精妙的十个知识点,并附上详细的实例代码。如能在实战中融会贯通、灵活使用,必将使代码更为精炼、高效,同时也会极大提升代码B格,使之看上去更老练,读起来更优雅。

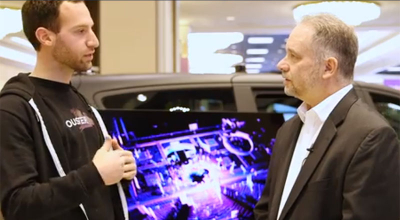

Ouster 是一家面向自动驾驶汽车、机器人、安全和地图绘制的领先高分辨率激光雷达传感器供应商,在拉斯维加斯 2020 国际消费电子展上展示了其全系列由 Xilinx 技术提供支持的数字 LiDAR 传感器。Xilinx 汽车解决方案总监 Paul Zoratti 采访 Raffi Mardirosian,介绍了 Xilinx FPGA 技术在 Ouster LiDAR 架构中的应用

关键内容提要:

(1) FPGA IO命名方式;

(2) FPGA的上电时序

今天想和大家一起聊聊FPGA的IO。

了解如何使用 Vivado HLS 可视化数据流设计的专用波形。这些波形轨迹有助于确认数据流已实现的并行性。

2 月中旬,国产手机品牌小米发布新款旗舰小米 10 系列,其主打卖点之一便是支持一亿像素 8K AI 视频拍摄。而在此之前率先面世的三星 Galaxy S20,更可以原生拍摄 8K 视频。从体型庞大的摄像机到如今一手可握的智能手机,技术的日益革新推动设备不断变化衍进,但 8K 却从未改变。

Xilinx FFT IP介绍:缩放因子等参数应该注意的matlab数据比对细节。

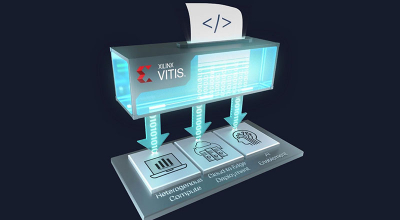

Vitis 平台将19.1之前的SDK、SDSoC、SDAccel整合在一起的基础上,加入了Vitis AI开发环境。让软件工程师也能够基于Vitis平台完成Xilinx器件的项目设计。然而对于习惯了传统的开发方式的工程师来说,最基本的嵌入式开发都要转移到Vitis上进行。本次我们就来看看从基础的SDK到Vitis有多少异同

从 2019.2 版开始,赛灵思 SDK 开发环境已统一整合到全功能一体化的 Vitis™ 统一软件平台中。尊敬的 SDK 用户,您只需轻点几下鼠标即可体验这一功能丰富的工具!