如何在数据中心部署深维FPGA+CPU图像处理解决方案

judy 在 周三, 03/11/2020 - 11:08 提交

实现了技术方面的突破,那么要如何与生产环境集成呢?如何在实际的业务体系中实现对FPGA优势更好的应用?实际部署是其中最值得探讨与研究的方向。对此,深维科技进行了一系列的探索与尝试,形成了以下几种方案

实现了技术方面的突破,那么要如何与生产环境集成呢?如何在实际的业务体系中实现对FPGA优势更好的应用?实际部署是其中最值得探讨与研究的方向。对此,深维科技进行了一系列的探索与尝试,形成了以下几种方案

ZYNQ中包含了两个部分,双核的arm和FPGA。根据XILINX提供的手册,arm模块被称为PS,而FPGA模块被称为PL。ZYNQ内部包含PS和PL两部分,ZYNQ开发有一下四种方式

EdgeBoard是基于FPGA打造的嵌入式AI解决方案,能够提供强大的算力,并支持定制化模型,适配各种不同的场景,并大幅提高设备的AI推理能力,具有高性能、高通用、易集成等特点

当调制方式为16-AQM,64-QAM和256-QAM时需要做位交织,交织的目的是将突发的错误分散开来,把一个较长的突发差错离散成随机差错,再用随机差错的编码(FEC)等信道编码技术消除随机差错,提高通信的可靠性。交织的越深,抗突发错误的能力也越强

在上一篇ZCU106 XRT环境搭建【Xilinx Vitis】中,我参考了XRT中其它平台(ZCU102,ZCU104)的Vivado TCL脚本,同时参考了官方的VCU相关工程,编写了ZCU106 XRT的脚本。在这篇文章中将对该工程进行一下分析。

学艺不精的后果就在于:学而不思则罔。圣人太厉害了,总结得很到位。比如最近项目中涉及到浮点和定点的转换,自己就有点蒙,边看边实验,还算理解了,作文以记之

最近有朋友问,公众号为什么起名叫网络交换FPGA?今天这篇文章就来回答一下。我们将从网络交换的历史讲起,也正如机器学习也赶上了ASIC工艺发展才引起革命性的变化一样。技术发展的历程中,总有那些看似不相关的技术结合起来,结果导致翻天覆地的变化

近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq®、Zynq MP、MicroBlaze™ 和全新的 Versal™ 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。

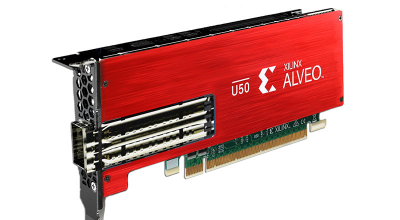

赛灵思 Alveo™ U50 数据中心加速器卡采用单插槽、小外形尺寸被动散热卡,运行时最大功耗限制为 75W。它支持PCI Express® (PCIe®) Gen3 x16 或双 Gen4 x8,配备 8 GB 高带宽存储器 (HBM2) 和以太网网络功能

Xilinx Floating-Point IP