赛灵思:有“野心”的半导体帝国缔造者

judy 在 周二, 07/23/2019 - 08:48 提交

要说在FPGA领域的地位,绝对没有哪家企业可以撼动赛灵思,毕竟FPGA就是人家发明的,而赛灵思的“野心”绝不止于此。除了发明FPGA,它还推出了许多项第一:第一家Fabless公司;第一个嵌入式处理器的FPGA;第一个3D架构的FPGA;第一个HLS开发工具Vivado;第一个ASIC+UltraScale架构FPGA

要说在FPGA领域的地位,绝对没有哪家企业可以撼动赛灵思,毕竟FPGA就是人家发明的,而赛灵思的“野心”绝不止于此。除了发明FPGA,它还推出了许多项第一:第一家Fabless公司;第一个嵌入式处理器的FPGA;第一个3D架构的FPGA;第一个HLS开发工具Vivado;第一个ASIC+UltraScale架构FPGA

Xilinx Spartan-7 SP701评估套件包含评估和评估所需的所有硬件,工具和IP开发您的Spartan-7 FPGA设计。 本指南提供了运行SP701内置自检(BIST)的说明并安装Xilinx工具。

全国高校自动化类专业教学论坛将于2019年8月6-8日在沈阳举行(详情链接 http://www.edu-forum.cn/zdhyxb/ ),此次活动主要围绕自动化, 机器人,人工智能这几大方向举行。Xilinx受邀在此次活动中就Xilinx相关技术进行分享。

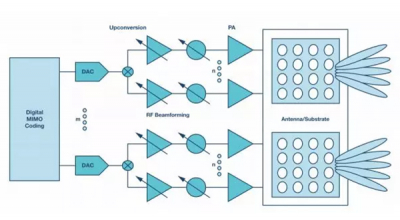

自80年代初引入模拟蜂窝网络以来,蜂窝通信已有了长足发展。如今,随着市场由4G向5G网络解决方案迁移,蜂窝通信行业正在为实现更快数据传输速度、更低延迟以及容量、用户密度和可靠性的巨大飞跃奠定基础。例如,5G不仅可以提高数据速率(100倍)和网络容量(10倍)

带宽是影响FPGA加速器的重要因素,因为大量的并行计算对数据量要求很大。如果加速器对数据的访问是不规则的,那么cache miss就会大大影响加速器性能。这篇来自FPGA2019会议的报告,向我们展示了如何来更好的处理cache miss问题,提高对缓存的利用率以及提高加速器效率

本文简要描述基于FPGA和万兆网的GigE Vison IP设计方案。GigE Vison协议基于普通的以太网物理链路,运行在UDP协议层之上,包含控制协议GVCP和数据流协议GVSP两大部分,整个层次结构如下图1所示

从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。在我们开始讨论增量综合之前,我们先来讨论一下一些重要的概念,以便能够更好地理解该流程。

Zebra 可消除深度学习推断中具有挑战性的编程及 FPGA 任务。Zebra 可轻松部署和适应广泛的神经网络及框架。

贸泽电子宣布与自适应和智能计算领域的知名厂商Xilinx签订了全球分销协议,即日起分销Xilinx产品,并提供开发软件和IP产品的在线下载。Xilinx是FPGA、硬件可编程片上系统 (SOC) 和自适应计算加速平台 (ACAP) 的发明者,致力于提供业内最具活力的处理器技术,打造未来自适应、智能化的互联世界

本系列前面几篇介绍了lwIP的相关知识和官方给出的应用实例。从本文开始将进入“实操”阶段,详细介绍Zynq如何使用UDP和TCP两种协议进行通信。建议阅读本文前先了解lwIP相关知识,重复的内容在本文只会简单讲述。