InAccel 的加速机器学习解决方案

judy 在 周五, 07/12/2019 - 10:22 提交

使用逻辑回归、K 均值和交替最小二乘法加速您的 Apache Spark 应用。 AML 是 InAccel 的加速机器学习库。旨在维护其它开源框架(如 Apache Spark)简单易用的实用接口,同时加速机器学习模型的训练环节。现在 AML 拥有所有所需的库,可训练您的逻辑回归和 Kmeans 模型

使用逻辑回归、K 均值和交替最小二乘法加速您的 Apache Spark 应用。 AML 是 InAccel 的加速机器学习库。旨在维护其它开源框架(如 Apache Spark)简单易用的实用接口,同时加速机器学习模型的训练环节。现在 AML 拥有所有所需的库,可训练您的逻辑回归和 Kmeans 模型

Xilinx的FIR的COE文件应该是这样的:

fileID = fopen('fir_h.coe','w');

fprintf(fileID,'%s\n%s\n','radix=10;','coefdata=');

fprintf(fileID,'%.0f,\n',h);

fclose(fileID);

radix=10;

coefdata=

-809,

-1746,

-1540,

1874,

9528,

19918,

29092,

32767,

29092,

19918,

9528,

1874,

-1540,

-1746,

-809;

无线设备和其处理的数据量每年都呈指数递增(53% 复合年增长率。随着这些设备产生并处理的数据量越来越多,连接这些设备的无线通信基础设施也必须持续发展才能满足需求。如图 1 所示,4G 网络频谱效率的提高已经不足以提供 3GPP[2] 定义的三大高级 5G 用例所需数据速率的阶梯函数了

Verilog HDL (Hardware Description Language) 是一种硬件描述语言,可以在算法级、门级到开关级的多种抽象设计层次上对数字系统建模。它可以描述设计的行为特性、数据流特性、结构组成以及包含响应监控和设计验证方面的时延和波形产生机制

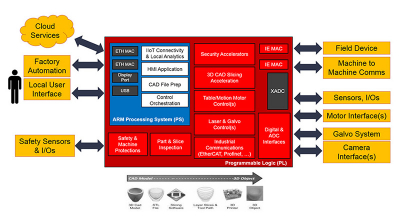

3D 打印领域正在材料与工艺、速度与复杂性,以及从制造商到大规模制造的商业模式等多个领域迅速发展。Xilinx SoC 和 FPGA 可为 3D 打印机设计人员和最终用户提供大量决定性优势

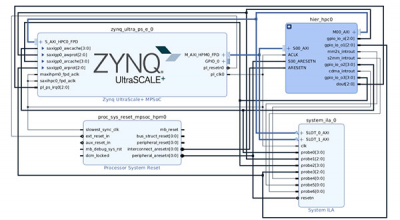

为了使相关传输被CCI监听,需要设置寄存器lpd_apu的最低两位为1,而且必须在A53处于复位态时设置。我们利用MPSoC BootROM在加载时设置寄存器lpd_apu。

为了用MPSoC BootROM在加载时设置寄存器lpd_apu,需要准备寄存器初始化文件,并且使用寄存器初始化文件创建启动文件boot.bin

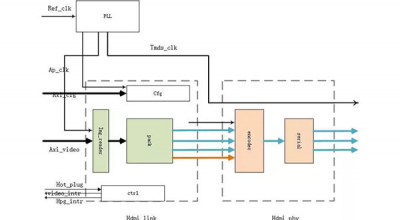

做图像处理没有显示怎么能行,所以用两章来介绍HDMI的协议以及编码实现。HDMI的编码,仿真和调试会花费较长时间,特别是第一次在windows环境下部署UVM环境,对于刚刚入门UVM的我来说,这块也花费了很长时间。截止目前设计和仿真的代码都已经做完。所以这章主要介绍HDMI的协议以及设计的架构,之后再用一章来介绍HDMI的实现和驱动编写

当下,数字经济蓬勃发展,作为驱动数字经济发展的技术推动力——5G和AI也在不断革新。作为FPGA的发明者,赛灵思公司将企业使命定位为“打造灵活应变,万物智能的世界”,致力于通过公司的转型和全新类型产品的打造,赋能所有的创新者以高性能且灵活应变的智能计算平台,加速其创新事业

近期有大量面向软件定义无线电 (SDR) 应用设计的新型 RF 采样数据转换器被开发出来,但是传统数据转换器使用的参数不能完整地特征化 RF 采样转换器。白皮书将一并介绍传统数据转换器和新型 RF 采样数据转换器的规格,同时提出适用于 RF 采样转换器的参数。

本指南适用于希望使用 SDAccel 开发环境创建 FPGA 加速应用程序的软件开发者和 RTL 设计师。它向开发者介绍了基于 FPGA 加速的基本概念,并描述了以最佳性能加速应用程序的逐步方法。