Spartan-7 SP701 FPGA 评估套件

judy 在 周二, 07/16/2019 - 08:26 提交

SP701 评估套件配备业界最佳性能功耗比 Spartan®-7 FPGA,适用于需要传感器融合的设计,如工业网络、嵌入式视觉和汽车等应用。SP701 通过 Pmods 和 FMC 连接器提供高 I/O 可用性和 I/O 扩展,使其成为 Spartan-7 FPGA 用户最大的 IP 开发平台。所包含的 XC7S100 FPGA 是 Spartan-7 系列中密度最大的器件。

SP701 评估套件配备业界最佳性能功耗比 Spartan®-7 FPGA,适用于需要传感器融合的设计,如工业网络、嵌入式视觉和汽车等应用。SP701 通过 Pmods 和 FMC 连接器提供高 I/O 可用性和 I/O 扩展,使其成为 Spartan-7 FPGA 用户最大的 IP 开发平台。所包含的 XC7S100 FPGA 是 Spartan-7 系列中密度最大的器件。

使用 Xilinx 深度学习处理器(DPU)IP 构建自定义系统,使用面向 Xilinx SoC 的 DNNDK 优化经过训练的推断模型。

Xilinx 计算库提供加速数学、统计、线性代数、金融函数和预构建定价模型,帮助开发人员快速构建各种加速应用。代码是开源的,可根据需要修改。

本篇完成对HDMI显示代码的UVM仿真,梳理一下在windows-modelsim工具下UVM仿真环境的建立,调试以及遇到的问题。仿真的架构在上一篇已经做了简要介绍,这部分做重点讲解

本文档描述了 Vivado 2019.1 中 PCI Express 内核的 UltraScale+ FPGA Gen3 集成块中集成的易用性特性。这些特性将在截图中详细介绍,以帮助用户更轻松理解其实现方案和用途。

文章阐述了Xilinx FPGA可编程的本质,逆向分析破解了FPGA编程的bit流文件,并将其与FPGA内部电路相对应,对于深度理解动态可编程及FPGA电路结构具有重要的指导价值,LUT动态可编程使得FPGA内部的资源使用起来更灵活,你可以把LUT当成BRAM使用,也可以随时改变若干个LUT组成电路完成的硬件功能

本篇作为xilinx 7系列FPGA简介篇的最后一篇,咱们来介绍MGT(Multi-gigabittransceiver)

深度神经网络(deep nearal network)是机器学习发展20年来取得的最大突破,比如在语音识别方面,相比于传统方法,其将错误率降低了30%;而在2011年的图片识别竞赛上,将错误率从26%降低到3.5%,这些使得处于发展低谷的人工智能突然热门起来,从学术界扩展到工业界,甚至在google的alpha go击败了顶级围棋大师李世石后,人工智能成为全民讨论的热门,所有的程序员都梦想转行机器学习

自比特币诞生之后,PoW挖矿作为最主流的共识机制已经运行了十年有余,而近年来由于挖矿造成的巨大能源消耗、算力逐渐集中于几大矿池而趋向中心化,以及挖矿设备相对较高的准入门槛使得越来越多的人转向新的共识机制,如PoS、DPoS、PoC等等

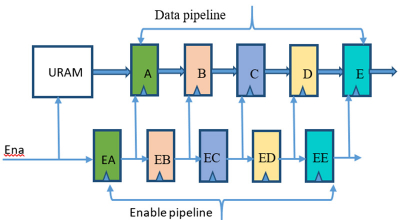

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。URAM 原语具有实现高速内存访问所需的可配置流水线属性和专用级联连接。 流水线阶段和级联连接是使用原语上的属性来配置的。 本篇博文描述的是通过将 URAM 矩阵配置为使用流水线寄存器来实现最佳时序性能的方法。