【网上研讨会】如何从海量的非结构化数据中提取和分析关键信息?

judy 在 周四, 07/25/2019 - 08:58 提交

通过本次研讨会,我们将为您分析大数据时代海量非结构化文本所带来的各种挑战, 为您详细介绍基于赛灵思全球最快数据中心加速卡的 SumUp Nucleus 文本分析平台, 并通过实际案例展示如何利用这个平台帮助企业或者个人快速从浩如烟海的文本中识别、提取和分析关键信息,从而为决策、战略或者传播监测提供强大支持

通过本次研讨会,我们将为您分析大数据时代海量非结构化文本所带来的各种挑战, 为您详细介绍基于赛灵思全球最快数据中心加速卡的 SumUp Nucleus 文本分析平台, 并通过实际案例展示如何利用这个平台帮助企业或者个人快速从浩如烟海的文本中识别、提取和分析关键信息,从而为决策、战略或者传播监测提供强大支持

本实例内容为PLL的配置和例化,通过PLL产生4个不同频率的时钟,分别驱动 4 个 LED 指示灯闪烁一样的频率。通过观察这 4 个 LED 指示灯的闪烁同步与否,可以确认 PLL 产生的这 4 个时钟的频率关系。

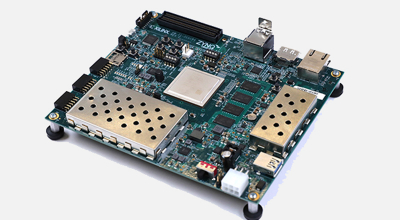

Zynq® UltraScale+™ RFSoC ZCU1285 特性描述套件提供您对集成型 ADC 和 DAC 以及 Zynq UltraScale+ Gen 2 XCZU39DR RFSoC 上提供的 GTY 和 GTR 收发器进行特性描述和评估时所需的一切。所有 16 个 12 位 2.220GSPS ADC、所有 16 个 14 位 6.554GSPS DAC、所有 16 个 GTY 收发器以及所有 4 个 GTR 收发器都可通过 Samtec BullsEye 连接器访问

看完一条微博/微信要多久?100条呢?1000条呢?8000条呢?看完再整理出高效的数据分析和见解呢?近期,美国 SumUP 分析公司利用其研发的实时文本分析平台,对美国总统特朗普就职以来的 8,000 多条 Twitter (英文的微博)推送进行了分析和处理,全程仅用 20 秒,秒杀的节奏!

提示和技巧总是非常有用的,在编程领域更是如此。有时候,小小的黑科技可以节省你大量的时间和精力。一个小的快捷方式或附加组件有时会是天赐之物,可以成为实用的效率助推器。所以,我在这里介绍下自己编程时最喜欢使用的一些提示和技巧,在这篇文章中汇总起来呈现给大家

本篇以ADI公司的多通道高速ADC—AD9639为实例,向大家演示FPGA是如何通过SPI协议向该ADC读写寄存器配置数据的。如下图所示为AD9639的功能框图,不难发现其SPI接口既可以实现三线模式也可以实现四线模式,本篇将演示4线模式

Silexica芯登科技发布了2019.2版的SLX开发工具,新版本对FPGA和C/C ++两大产品性能进行了重大改进。当开发人员在为Xilinx®Vivado®HLS设计流程 时,SLX FPGA所提供的优化C / C ++代码能够帮助其向HLS(高层次综合)做好准备。其中新加自动插入HLS编译指示功能将HLS的性能平均提升35倍(与没有HLS编译指示功能的版本相比)

面向 SDSoC 的 DNNDK 用户指南

图像增强就是通过一定手段来增强图像的对比度,使得其中的人物或者事物更加明显,有利于后边的识别等处理。本章介绍几个传统的图像增强算法,并给出matlab实现代码,看一看不同算法的实现效果,最后再介绍一下深度学习在图像增强上的应用

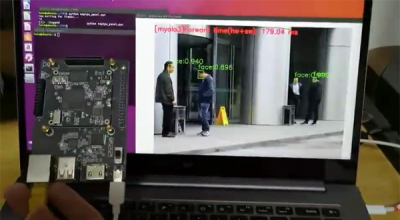

本人有过多年用FPGA做图像处理的经验,在此也谈一下自己的看法。用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性。因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA。例如在一些分选设备中图像处理基本上用的都是FPGA