Virtex UltraScale+ 56G PAM4 VCU129 FPGA 评估套件

judy 在 周二, 06/25/2019 - 14:59 提交

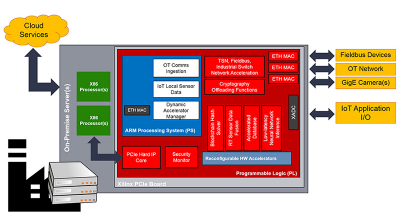

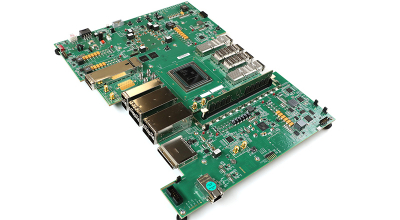

VCU129 开发板整合了集成 PAM4 收发器的 Virtex® UltraScale+™ 58G PAM4 VU29P FPGA,可实现新一代网络平台。VCU129 评估套件展示了 Xilinx SerDes 技术的领先地位,可充分利用 Xilinx 无盖封装方法的低成本散热设计。VCU129 具有多种通用高速互连、板载内存和 PCIe®Gen 3 接口。