基于FPGA 视网膜机理的色调映射处理器

judy 在 周五, 05/24/2024 - 10:10 提交

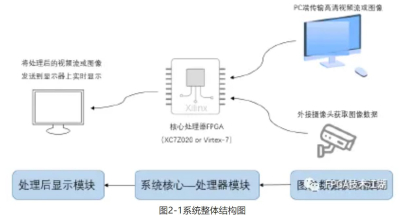

本篇所设计的处理器在以XC7Z020芯片为基础的PYNQ-Z2的平台上处理256*180的高清图像,可以达到700帧的实时速率

本篇所设计的处理器在以XC7Z020芯片为基础的PYNQ-Z2的平台上处理256*180的高清图像,可以达到700帧的实时速率

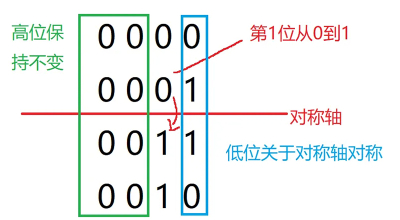

格雷码是美国学者Frank Gray于1947年提出的一种二进制编码方式,后面这种编码方式就以他的名字命名

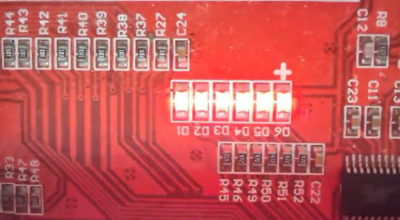

呼吸灯在日常生活中经常见到,如电子时钟,小夜灯等等,本文我们介绍下通过PWM波来控制LED灯,实现呼吸灯功能

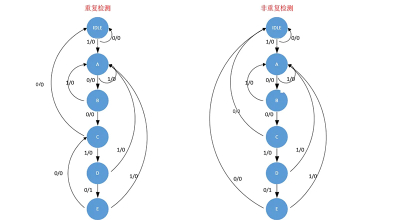

序列检测器指的就是将一个指定的序列(以‘10010’为例)从数字码流中识别出来,是一个经典的数字电路实例

本文描述了一种简单高效配置FPGA的方法,该方法利用微处理器从串行外围接口(SPI)闪存配置FPGA设备。这种方法减少了硬件组件、板空间和成本。

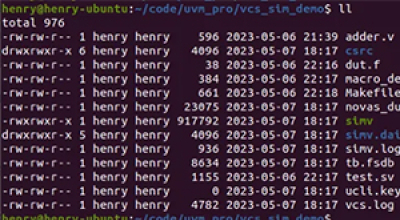

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

本文我们介绍UART通信协议、传输时序及如何利用HDL编程实现FPGA与PC通信。

在介绍skid buffer之前,我们先来假设这样一种情况,在一个多级流水模型之中,比如最为经典的顺序五级流水的处理器模型中

在电路设计中,相信大家总见到上拉电阻和下拉电阻这两个名字,但是不知道各位对他们有没有详细的了解,咱们今天就来聊聊上拉、下拉电阻那点事

DDR4 SDRAM因其高速、大容量的特点,在FPGA设计中扮演着越来越重要的角色。本文将详细介绍DDR4 MIG IP核及其配置过程。