Quartus中的逻辑锁定与增量编译

judy 在 周二, 06/11/2024 - 14:45 提交

逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。

逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。

很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗?

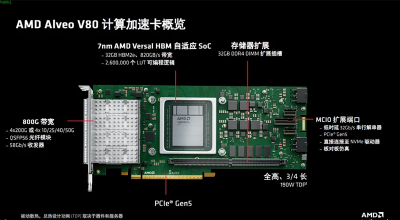

图形处理单元 (GPU) 和现场可编程门阵列 (FPGA) 是用于成像和其他繁重计算的三种主要处理器类型中的两种

此文针对一个MultiBoot应用案例做一些深入探讨,需要读者比较熟悉FPGA的MultiBoot设计流程

本文介绍使用Intel Quartus Prime和Xilinx Vivado生成和保护网表代码的一般步骤

本文通过以LCD1602液晶显示模块为基础,介绍FPGA驱动LCD1602原理,详细介绍硬件原理图设计及FPGA驱动LCD1602软件设计

6月12日至14日易灵思将亮相上海世博展览馆3号馆的“智慧赋能 科技全球”2024上海国际嵌入式展

易灵思(深圳)科技有限公司与成都信息工程大学电子工程学院签署了院校合作协议,双方希望通过此次合作,共同推动FPGA技术的发展和人才的培养。

DisplayPort图像显示接口不仅传输率高,而且可靠稳定,其接口传输的信号由传输图像的数据通道信号以及传输图像相关的状态