带你快速入门AXI4总线--AXI4-Lite篇(2):XILINX AXI4-Lite接口IP源码仿真分析(Slave接口)

judy 在 周二, 02/07/2023 - 11:07 提交

在这篇文章中,我们照葫芦画瓢,也打包2个AXI4-Lite接口的IP,来对其的仿真和原始代码学习一番

在这篇文章中,我们照葫芦画瓢,也打包2个AXI4-Lite接口的IP,来对其的仿真和原始代码学习一番

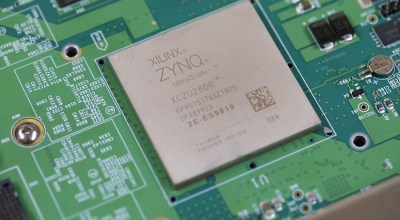

Zynq UltraScale+ MPSOC在PS侧扩展了PS-GTR接口,可以灵活的支持PCIe、SATA和USB3.0连接

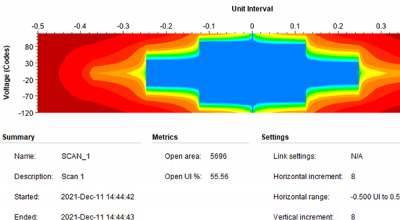

之前我们在讲serdes的时候讲到了使用in-system-ibert来进行眼图的扫描

该系列先对AXI4-Stream协议及其使用做一个简单的介绍

本项目主要是设计AI加速器,利用Xilinx的CDMA加载权重,输入到PL区的Block Ram

本文概述了如何在系统中使用RFSoC 射频数据转换器的自动增益控制和NCO跳频功能。

使用AMD、RFDSP、VIAVI和Rohde & Schwarz的设备演示基于Zynq RFSoC DFE的O-RAN前传和射频合规性

一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时

这个算法对图像有一定的包边去噪效果,在FPGA上实现起来复杂度较低

今天给大家分享下高速ADC噪声系数计算方法