赛灵思/GTX高速接口通关简介

wyh102 在 周一, 12/19/2022 - 10:20 提交

SATA 接口只有几根线为什么那么示的10Gbps(万快?连上网线显兆网)是很令人是不兴奋

SATA 接口只有几根线为什么那么示的10Gbps(万快?连上网线显兆网)是很令人是不兴奋

什么是FPGA? 我们的FPGA有个中文名称叫“现场可编程的门阵列”,这又是一个什么概念呢?

Xilinx Vitis AI 提供了一个工作流程,使用简单的流程在 Xilinx 深度学习处理单元上部署深度学习推理应用

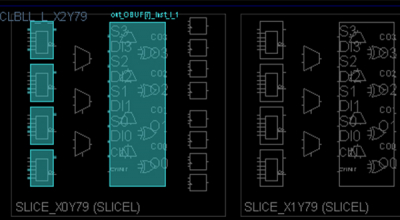

本文介绍RTL分析、综合、实现的具体含义和区别

Xilinx处理器系统复位模块允许客户通过设置某些参数来启用/禁用功能,从而根据自己的应用来定制设计

本文参考官方手册,主要对RFSoC ADC的数字数据路径相关功能进行介绍。

对于工业企业而言,推进数字化转型至关重要,以此才能保持竞争力,并为客户提供价值

Xilinx越来越多的例程,给出的参考设计是基于Block Design设计方法的

本文我们继续介绍FPGA收发器TX结构和功能。

在日常的编码过程中,常常碰到一个参数会被到处调用的情况,比如时钟的定义和调用